# (12)公開特許公報(A)

1

(19)日本国特許庁(JP)

(11)特許出願公開番号"

特開平6-130910

(43)公開日 平成6年(1994)5月13日

| (51)Int.Cl. <sup>5</sup> |       | 識別記号 | 庁内整理番号   | FI | • | 技術表示箇所 |

|--------------------------|-------|------|----------|----|---|--------|

| G 0 9 G                  | 3/20  | R    | 7335—5 G |    |   |        |

| G02F                     | 1/133 | 545  | 9226-2K  |    | , |        |

| G 0 9 G                  | 3/36  |      | 7319—5 G |    |   |        |

審査請求 未請求 請求項の数10(全 28 頁)

| (21)出願番号    | 特願平5-152533     | (71)出願人 000002369                      |

|-------------|-----------------|----------------------------------------|

| (22)出願日     | 平成5年(1993)6月24日 | セイコーエブソン株式会社<br>東京都新宿区西新宿 2 丁目 4 番 1 号 |

|             |                 | (72)発明者 今村 陽一                          |

| (31)優先権主張番号 | 特願平4—179997     | 長野県諏訪市大和3丁目3番5号 セイコ                    |

| (32)優先日     | 平4(1992)7月7日    | ーエブソン株式会社内                             |

| (33)優先権主張国  | 日本(JP)          | (74)代理人 弁理士 山田 稔                       |

|             |                 |                                        |

|             |                 |                                        |

(54)【発明の名称】。マトリクス型表示装置。マトリクス型表示制御装置及びマトリクス型表示駆動装置

(57)【要約】 (修正有)

【目的】 表示データの転送方式を改善し、低消費電力 が少く大容量表示に適したマトリクス型表示制御装置を 提供する。

【構成】 モジュール・コントローラ100は、低周波 発振回路110、その低周波クロック  $f_L$ を基に走査ス タート信号YD等を生成するタイミング信号発生回路1 20、ホストMPU10との通信とシステムバス14a を監視しVRAM12内の表示データ更新に対し間欠動。 作開始制御信号STを作成するスタンバイ回路130、 低周波クロック  $f_L$ に位相同期する高周波クロックを作、 成する高周波発振回路140、VRAM12から専用バ ス14bを介して表示データをダイレクトメモリアクセ スで読み出し、データバス17を介してXドライバ25: 0-1~250-Nのフレームメモリ252へ転送する DMA回路150を有している。

【特許請求の範囲】

【請求項1】 表示画素がマトリクス状に配列されたマ トリクス型表示体と、表示データを記憶する随時書込み 読み出し可能の第1の記憶手段と、該表示画素の少なく とも一部に対応する表示データを記憶する随時書込み読 み出し可能の第2の記憶手段と、第2の記憶手段から表 示データを読み出し前記マトリクス表示体の信号電極に 駆動電圧を印加する信号電極駆動手段とを有するマトリ クス型表示装置において、前記第1の記憶手段に記憶さ れた表示データの変更により発振する間欠動作型高周波 発振手段と、該間欠動作型高周波発振手段からの高周波 クロックを用いて前記第1の記憶手段から前記変更に係 る表示データを読み出してこれと前記高周波クロックを 前記第2の記憶手段側へ転送する表示データ転送手段と を有することを特徴とするマトリクス型表示装置。

【請求項2】 第1の記憶手段に記憶された表示データ の変更により発振する間欠動作型高周波発振手段と、該 間欠動作型高周波発振手段からの高周波クロックを用い て前記第1の記憶手段から前記変更に係る表示データを 読み出しこれと前記高周波クロックを第2の記憶手段側 へ転送する表示データ転送手段とを有することを特徴と するマトリクス型表示制御装置。

【請求項3】 低周波数クロックを常時発振する低周波 発振手段と、該低周波発振手段からの低周波数クロック を基に所要タイミング信号を生成するタイミング信号発 生手段と、第1の記憶手段に記憶された表示データの変 更により間欠動作制御信号を発生する表示データ更新検 出手段と、該間欠動作制御信号により発振する間欠動作 型高周波発振手段と、該間欠動作型高周波発振手段から の高周波クロックを用いて前記第1の記憶手段から前記 30 変更に係る表示データを読み出しこれと前記高周波クロ ックを第2の記憶手段側へ転送する表示データ転送手段 とを有することを特徴とするマトリクス型表示制御装 置。

【請求項4】 マトリクス型表示体の表示画素の少なく とも一部に対応する表示データを記憶する随時書込み読 み出し可能の第2の記憶手段を有し、第2の記憶手段か ら表示データを読み出し前記マトリクス表示体の信号電 極に駆動電圧を印加するマトリクス型表示駆動装置にお いて、1走査期間毎に受け取る周期信号を基に1走査期 40 間でタイミングをずらした書込み制御信号及び読み出し 制御信号を生成するタイミング発生手段と、前記第2の 記憶手段の同一行アドレスに対する読み出し制御信号によ り読み出し動作を実行した後前記書込み制御信号によ り書込み動作を実行する書込み読み出し手段を有するこ とを特徴とするマトリクス型表示駆動装置。

【請求項5】 請求項4に記載のマトリクス型表示駆動 装置において、前記表示データの転送に用いられる高周 波クロックの動作停止を検出するクロック検出手段を有 し、この検出信号により前記書込み制御信号の発生を阻 50

止する書込み禁止制御手段とを有することを特徴とする マトリクス型表示駆動装置。

【請求項6】 請求項5に記載のマトリクス型表示駆動 装置において、前記書込み読み出し手段は、入来する表 示データを前記高周波クロックを順次用いて少なくとも 1走査ライン分格納する一時格納手段と、該一時格納手 段の格納表示データを前記高周波クロックの1周期以上 の長い信号により前記第2の記憶手段に書込み供給する バッファッ手段を有することを特徴とするマトリクス型 10 表示駆動装置。

【請求項7】 請求項4至請求項6のいずれか一項に記

載のマトリクス型表示駆動装置において、書込み読み出 し手段は、前記第2の記憶手段から読み出した表示デー タと前記マトリクス表示体の走査電極の電圧状態とから 前記信号電極に印加すべき信号電圧を割り出す信号電圧 状態割り付け手段を有することを特徴とするマトリクス 型表示駆動装置。

【請求項8】

請求項7に記載のマトリクス型表示駆動 装置において、前記信号電圧割り付け手段は、前記第2

の記憶手段から複数の走査ライン分の表示データを時分 割で読み出す手段と、読み出された表示データを相互に 待ち合わせる一時記憶手段と、前記マトリクス表示体の 走査電極の電圧状態を指定する走査状態指定手段と、読 み出された複数の走査ライン分の表示データと走査電極 の選択電圧状態とから駆動電圧を選択する電圧選択手段 とを有することを特徴とするマトリクス型表示駆動装 置。

【請求項9】 請求項7に記載のマトリクス型表示駆動 装置において、前記第2の記憶手段は、1行アドレスに 対し前記マトリクス表示体の複数の走査ライン分の表示 データを格納するメモリ配列を有しており、前記信号電 圧状態割り付け手段は、前記複数の走査ライン分の表示 データを一挙に読み出す手段と、前記マトリクス表示体 の走査電極の電圧状態を指定する走査状態指定手段と、 読み出された複数の走査ライン分の表示データと走査電 極の選択電圧状態とから駆動電圧を選択する電圧選択手 段とを有することを特徴とするマトリクス型表示駆動装 置。

【請求項10】 マトリクス型表示体の走査電極を選択 して駆動するマトリクス型表示駆動装置において、複数 本の走査電極を同時に選択してフレーム開始信号の周期 内に複数回の巡回走査をする手段を有することを特徴と するマトリクス型表示駆動装置。

【発明の詳細な説明】

[0001]

【産業上の利用分野】本発明は、複数ライン同時選択駆動方式を採用するに好適な液晶表示装置等のマトリクス型表示装置に関し、更に詳しくは、主にマトリクス型表示素子モジュール・コントローラと信号電極ドライバ回路の改良に関する。

[0002]

【従来の技術】従来、フラットディスプレイの一例とし ての単純マトリクス型液晶表示装置においては、MPU (マイクロ・プロセッサ・ユニット) 側から表示データ をLCDモジュール(液晶表示パネル(LCDパネ ル)、走査電極駆動回路(Yドライバ),信号電極駆動 回路(Xドライバ)等)へ転送する方式として、マトリ クス型液晶表示素子モジュール・コントローラ(以下、 モジュール・コントローラと言う)を用いる方式とRA M (読み出し専用メモリ) 内蔵型X ドライバを用いる方 10 式とに大別できる。まず、前者の方式は、CRTを用い た表示装置と同様、システムバスに繋がるモジュール・ コントローラが表示データを記憶しているビデオRAM (VRAM) から表示データを読み出し、これをLCD モジュールに対し高周波数のクロックで転送して表示リ フレッシュ動作を行うものである。後者の方式は、Xド ライバ内に2ポートタイプのフレームメモリ(内蔵RA M)を持ち、MPUがデータバス、コントロールバス又 はアドレスバスを介して液晶表示タイミングとは無関係 に直接フレームメモリにアクセスし、フレームメモリ内 の表示データを変更するようになっており、Xドライバ 内で所要の制御信号を生成して、内蔵フレームメモリか ら一走査ライン分の表示データを同時に読み出し、表示 リフレッシュ動作を行うものである。

3

[0003]

【発明が解決しようとする課題】前者の方式において は、表示画面を変える度に、その液晶表示タイミングに 合わせてVRAMからの読み出しと転送を行うので、V RAM. モジュール・コントローラ、及び液晶ドライバ を高周波クロックで常時動作させておく必要がある。ま た表示リフレッシュ動作に関係する回路がVRAM, モ ジュール・コントローラ、及び液晶ドライバに亘る。こ の高周波クロックでの大規模回路の動作によると、回路 素子を構成する多数のCMOSに貫通電流等が生じ、消 費電力の増大に繋がり、大型LCDパネルを用いればそ れだけ増大する。またVRAMに対してはMPUのアク セスとモジュール・コントラーラのアクセスとがある が、表示リフレッシュ動作時のMPUのアクセスがMP Uのアクセスと衝突しないように高速クロックを用いな。 化には制約があると共に、MPU処理能力にも制約が付け く。後者の方式においては、液晶表示タイミングとは無 関係に表示データの転送が行われるので、低周波クロッ クでの動作が可能であり、前者の方式に比べて1~2桁 低い消費電力で済む。ところで、大型の液晶パネルを用 いる場合においては、Xドライバの個数を増やす必要が あるが、Xドライバの内蔵メモリ(RAM)はそれ自身 独立のアドレス空間を有しており、Xドライバの出力端。 子数は一般に2のべき数(2n)ではなく例えば160; ピン等の10の倍数であるので、MPU側から複数のX:50の記憶手段から変更に係る表示データを読み出しこれと

ドライバの内蔵メモリを見た場合、内蔵メモリ全体のア ドレスには離散的な空きが生じてアドレスの連続性が確 保されていない場合が多い。このため、スクロール動作 やパニング動作等の表示画面全体を同時に変更する時に は、MPU側でアドレス対応付けの処理を高速で行う必 要を余儀無くされ、MPUに大きな処理負担を強いるこ とになる。勿論、XドライバICの出力ピン数を2のべ き数にするように設計可能であるが、既存の液晶パネル の電極数との整合性が崩れてしまい、システムの互換性 を著しく損なう。また多数のXドライバを用いると、チ ップセレクト線等の本数が必然的に増え、液晶パネルの 周辺に配する多数のXドライバのスペースをその分確保 せねばならず、パネルの表示面積比の低下を招きLCD モジュールの小型化の障害になる。従って、後者の方式 は大規模の液晶パネルに適用するには不向きである。 【0004】そこで、上記各問題点に鑑み、本発明は、 表示データの転送方式を改善することにより、低消費電 カでありながら、大容量表示に適したマトリクス型表示 制御装置、マトリクス型表示駆動装置及びマトリクス型 表示装置を提供することにある。 20

[0005]

【課題を解決するための手段】上記課題を解決するため に、本発明の講じた手段は、従来のモジュール・コント ローラ型の表示装置と、従来のフレームメモリ内蔵型の 信号電極ドライバとを組合せた方式において、モジュー ル・コントローラの高周波クロックの発振源を表示デー タの転送の際に間欠動作させるようにしたことに特徴を 有する。即ち、本発明は、表示画素がマトリクス状に配 列されたマトリクス型表示体と、表示データを記憶する 随時書込み読み出し可能の第1の記憶手段と、表示画素 30 の少なくとも一部に対応する表示データを記憶する随時 書込み読み出し可能の第2の記憶手段と、第2の記憶手 段から表示データを読み出しマトリクス表示体の信号電 極に駆動電圧を印加する信号電極駆動手段とを有するマ トリクス型表示装置において、マトリクス型表示制御装 置を、第1の記憶手段に記憶された表示データの変更に より発振する間欠動作型高周波発振手段と、間欠動作型 、高周波発振手段からの高周波クロックを用いて第1の記 憶手段から前記変更に係る表示データを読み出してこれ ければならず、モジュール・コントローラの低周波動作 40 と高周波クロックを前記第2の記憶手段側へ転送する表 示データ転送手段とで構成した点に特徴を有する。この マトリクス型表示制御装置の具体的な構成は、低周波数 クロックを常時発振する低周波発振手段と、低周波発振 手段からの低周波数クロックを基に所要タイミング信号。 を生成するタイミング信号発生手段と、第1の記憶手段。 に記憶された表示データの変更により間欠動作制御信号。 を発生する表示データ更新検出手段と、間欠動作制御信系 \*号により発振する間欠動作型高周波発振手段と、間欠動、 作型高周波発振手段からの高周波クロックを用いて第1

5 高周波クロックを第2の記憶手段側へ転送する表示デー タ転送手段とを有するものである。

ζ.

【0006】このようなマトリクス型表示制御装置を有 する表示装置において、表示画素の少なくとも一部に対 応する表示データを記憶する随時書込み読み出し可能の 第2の記憶手段を有し、第2の記憶手段から表示データ を読み出しマトリクス表示体の信号電極に駆動電圧を印 加するマトリクス型表示駆動装置としては、1 走査期間 毎に受け取る周期信号を基に1走査期間でタイミングを るタイミング発生手段と、第2の記憶手段の同一行アド レスに対する読み出し制御信号により読み出し動作を実 行した後書込み制御信号により書込み動作を実行する書 込み読み出し手段を有するものである。

【0007】そして、このようなマトリクス型表示駆動 装置において、表示データの転送に用いられる髙周波ク ロックの動作停止を検出するクロック検出手段を有し、 この検出信号により書込み制御信号の発生を阻止する書 込み禁止制御手段とを有することが望ましい。

【0008】また、マトリクス型表示駆動装置の書込み 読み出し手段は、入来する表示データを髙周波クロック を順次用いて少なくとも1 走査ライン分格納する一時格 納手段と、一時格納手段の格納表示データを高周波クロ ックの1周期以上の長い信号により第2の記憶手段に書 込み供給するバッファッ手段を有することが望ましい。

【0009】複数ライン同時選択駆動方式を採用するマ トリクス型表示駆動装置においては、書込み読み出し手 段は、第2の記憶手段から読み出した表示データとマト リクス表示体の走査電極の電圧状態とから信号電極に印 加すべき信号電圧を割り出す信号電圧状態割り付け手段 を有することが必要となる。具体的な信号電圧割り付け 手段の構成の一例としては、第2の記憶手段から複数の 走査ライン分の表示データを時分割で読み出す手段と、 読み出された表示データを相互に待ち合わせる一時記憶 手段と、マトリクス表示体の走査電極の電圧状態を指定 する走査状態指定手段と、読み出された複数の走査ライ ン分の表示データと走査電極の選択電圧状態との不一致 数を判定する不一致数判定手段と、その不一致数に応じ た信号電圧を選択する電圧選択手段とを有する。また複 数同時選択駆動方式を採用する別のマトリクス型表示駆 動装置においては、第2の記憶手段が1行アドレスに対 しマトリクス表示体の複数の走査ライン分の表示データ を格納するメモリ配列を有しており、信号電圧状態割り 付け手段が、複数の走査ライン分の表示データを一挙に 読み出す手段と、マトリクス表示体の走査電極の電圧状 態を指定する走査状態指定手段と、読み出された複数の 走査ライン分の表示データと走査電極の選択電圧状態と から駆動電圧を選択する電圧選択手段とを有する構成を 採用できる。

【0010】また、複数ライン同時選択駆動方式を採用

する走査電極側駆動装置における均等分散型複数ライン 同時選択駆動に適した構成としては、本発明は、複数本 の走査電極を同時に選択してフレーム開始信号の周期内 に複数回の巡回走査をする手段を有することを特徴とす る。

[0011]

【作用】このようなマトリクス型表示制御装置によれ ば、第1の記憶手段において表示データの変更があった ときだけ高周波クロックが動作し、表示データを第2の ずらした書込み制御信号及び読み出し制御信号を生成す 10 記憶手段へ転送するものであるから、高周波クロックの 間欠動作により低消費電力化を図ることができる。また 第2の記憶手段に対する転送処理はMPUが行うのでは なく、仲介に立つマトリクス表示制御装置が実行するも のであるため、第1の記憶手段側のホストMPUの処理 負担を低減できると共に、更に信号電極の駆動装置をカ スケード接続することにより、ドライバ側のメモリ空間 を意識せずに、マトリクス型表示体の構成に合わせて表 示データの転送ができるようになり、アドレスの対応付 けの容易化も達成できる。そして、第2の記憶手段に走 査ライン毎の表示データが一挙に格納されるので、画面 20 変更の高速化を達成できる。更に、信号電極の駆動装置 のカスケード接続により大容量表示装置でもマトリクス 型表示制御装置と駆動装置との結線数(例えばチップセ レクト線の本数)を抑制でき、表示画面面積比率の大き

> な表示装置を実現できる。 【0012】また、信号電極ドライバにおいては高速ク ロックを用いないで1 走査期間を分割したタイミングで 第2の記憶手段に余裕を以てアクセスするようにしてあ る。

【0013】このため、第2の記憶手段へのアクセスタ イミングが従来に比して緩和されるので、書込み力を向 上させることができ、第2の記憶手段の構成トランジス タのサイズを縮小化できる。ドライバのチップサイズの 小型化にも寄与する。

[0014]

【実施例】次に、添付図面に基づいて本発明の実施例を 説明する。

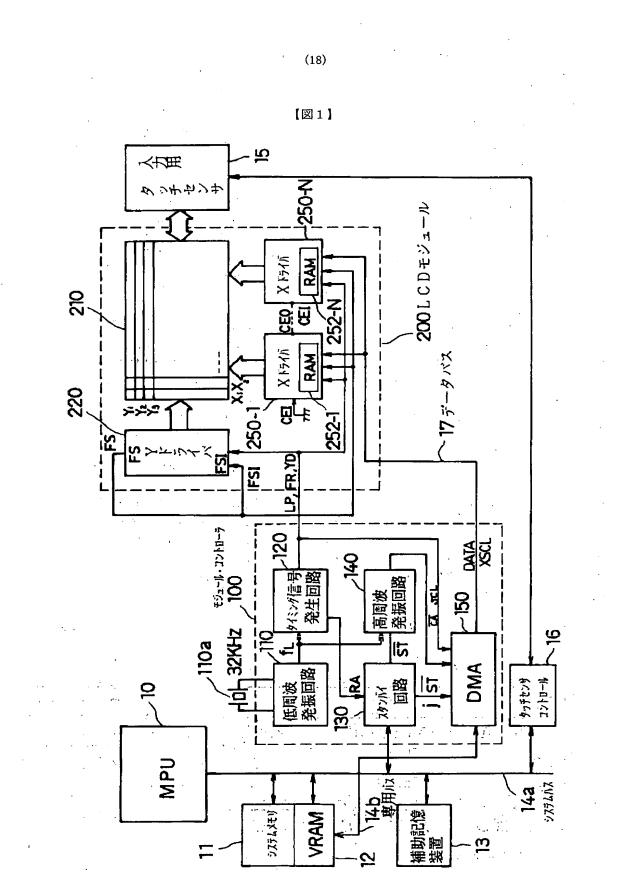

【0015】〔全体構成の説明〕図1は本発明の実施例 に係る単純マトリクス型液晶表示装置の全体構成を示す ブロック図である。この単純マトリクス型液晶表示装置 40 は、プログラムされたホストMPU10と、このMPU 10のワーキングメモリとなるシステムメモリ11と、 システムメモリ11と同一のアドレス空間に表示データ を格納するビデオRAM(VRAM)12と、画像,デ ータ及び音声情報等を記憶する補助記憶装置13と、シ ステムバス14a及び専用バス14bに繋がるモジュー ル・コントローラ100と、このモジュール・コントロ ーラ100により表示制御されるLCDモジュール20 0と、入力用タッチセンサ15と、タッチセンサ・コン トローラ16を有している。なお、システムバス14a 50

10

20

には、従来のコンピュータシステムと同様:通信制御装 置や他の表示装置等の周辺装置を必要に応じて接続する ことができる。LCDモジュール200は、単純マトリ クス型液晶表示パネル(LCDパネル)210と、その LCDパネル210の複数の走査電極Y<sub>1</sub>,Y<sub>2</sub>…を選択 する走査電極駆動回路(YドライバIC)220と、L CDパネル210の複数の信号電極に表示データを供給 するN個のフレームメモリ(RAM)内蔵型信号電極駆 動回路(XドライバIC)250-1~250-Nを有 している。

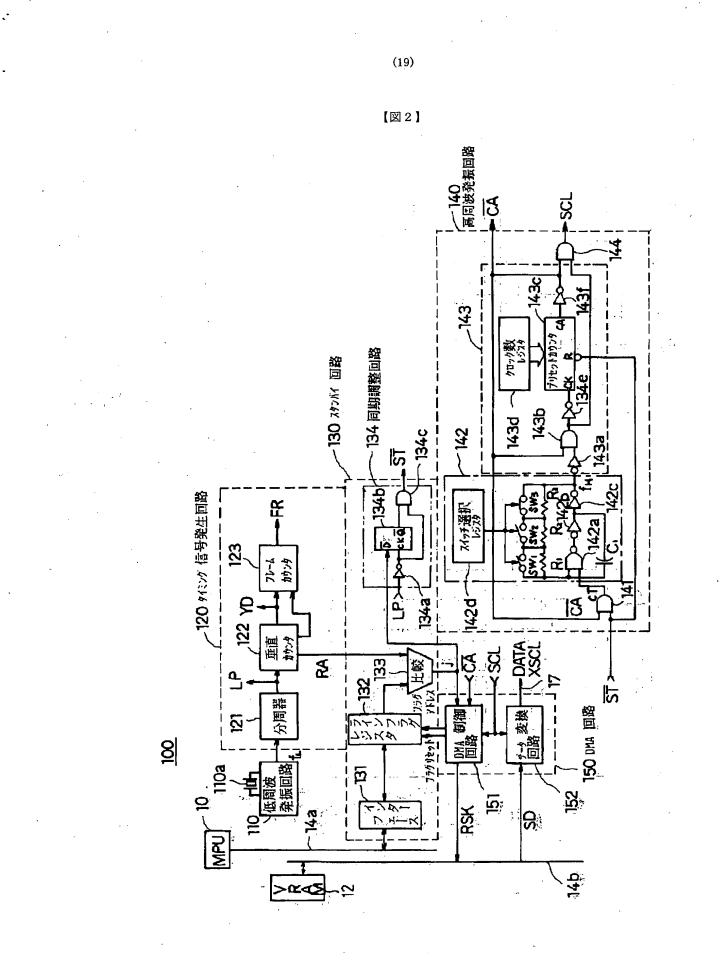

【0016】 [モジュール・コントローラの説明] モジ ュール・コントローラ100は、32KHz~512KHz 程度の振動子110aを持ち低周波クロックfLを常時 発振する低周波発振回路110と、その低周波クロック fLを基にLCDモジュール200に必要な走査スター ト信号(フレーム開始パルス)YD,転送表示データの 直並列変換用のラインラッチ信号(ラッチパルス)L

P,液晶交流化信号FR等を生成するタイミング信号発 生回路120と、ホストMPU10から間欠動作指示情 報を直接受領したとき又はホストMPU10との通信と システムバス14aを監視しVRAM12内の表示デー タの更新があったとき間欠動作開始制御信号ST(バ

400

ー)を作成するスタンバイ回路(表示データ更新検出回路)130と、間欠動作開始制御信号ST(バー)の印加期間において低周波クロックfLに位相同期する高周波クロックfHを作成する高周波発振回路140と、間欠動作開始制御信号ST(バー)の印加期間においてその高周波クロックfHを利用してVRAM12から専用バス14bを介して表示データをダイレクトメモリアクセス方式で読み出し、その表示データをデータバス17のビット数又はフォーマットに変換して表示データをそのデータバス17を介してXドライバ250-1~250-Nのフレームメモリ252-1~252-Nへ転送するダイレクト・メモリ・アクセス(DMA)回路15、0とを有している。

【0017】タイミング信号発生回路120は、図2に 示すように、低周波クロックflを基に1水平期間内に 2発のラッチパルス(ラインラッチ信号)LPを生成す る分周器121と、ラッチパルスLPを計数して走査電行 極の順番(行アドレス)を指定するための行アドレス信 号RA及びフレーム開始パルスYDを生成する垂直カウ ンタ122と、フレーム開始パルスYD及び垂直カウン タ122の所定カウント値に基づき液晶交流化信号FR を生成するフレームカウンタ123とを有している。ス タンパイ回路130は、システムバス・インターフェー ス回路131と、MPU10がVRAM12のうちXド ライバのフレームメモリの該当領域に表示データの変更 を加えたときMPU10によって転送指示フラグが立つ ラインフラグレジスタ132と、転送指示フラグが立つ た走査電極のアドレスと行アドレスRAとの一致/不一

教を判定し一致信号jを生成する比較回路133と、その一致信号jとラッチパルスLPとから間欠動作開始制「御信号ST(バー)を生成する同期調整回路134とを有している。ここで、ラッチパルスLPの1水平期間(1H)内での発生数は、後述する2ライン同時選択駆動方式の採用により2発である。同期調整回路134は、ラッチパルスLPを反転するインバータ134aと、ラッチパルスLPの立ち下がりに同期した一致信号を生成するD型フリップフロップ134bと、その同期一致信号のパルス幅をラッチパルスLPの周期に限定して間欠動作開始制御信号ST(バー)とする論理積ゲート134cとからなる。なお、VRAM12に対する読み出しスタートアドレスはホストMPU10によって予めセットされる。

【0018】高周波発振回路140は、間欠動作開始制

御信号ST (バー) 及び後述する間欠動作終了制御信号 CA (バー) から発振制御信号CTを作成する論理積ゲ ート141と、その発振制御信号CTを作成する論理積ゲ ート141と、その発振制御信号CTにより間欠発振す る高周波の可変周波数CR発振器142と、この高周波 の可変周波数CR発振器142で得られた高周波クロッ クf<sub>H</sub>を計数して間欠動作終了制御信号CA (バー)を 作成して間欠動作期間を限定する間欠動作時限回路14 3と、その高周波クロックf<sub>H</sub>と間欠動作時限回路14 3と、その高周波クロックf<sub>H</sub>と間欠動作終了制御信号 CA (バー) とから表示データのシフトレジスタ格納用 のシフトクロックSCLを作成する論理積ゲート144 とを有している。可変周波数CR発振器142は、論理 積ゲート142a, インバータ142b, 142c, 帰 還抵抗R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub> 及び帰還キャパシタC<sub>1</sub> からなるC R発振部と、抵抗選択スイッチSW<sub>1</sub>, SW<sub>2</sub>, SW<sub>3</sub>, と、

- MPU10により時定数がセットされてそれに応じた抵抗選択スイッチSW1,、SW2,SW3の開閉の組合せを行うスイッチ選択レジスタ142dとを有している。このスイッチ選択レジスタ142dの内容により抵抗選択スイッチSW1,SW2,SW3の開閉の組合せを変えることでCR発振部に寄与する帰還抵抗(時定数)が変わるので、CR発振部の発振周波数fHの値を可変できるようになっている。間欠動作時限回路143は、高周波クロックfHを反転バッファするインバータ143aと、間、欠動作終了制御信号CA(バー)の高レベル期間だけ高

- 10 周波クロック f<sub>H</sub>を通過させる論理積ゲート143b

と、論理積ゲート143bからの高周波クロック f<sub>H</sub>を インバータ143eを介してクロック入力とし間欠動作

開始制御信号ST(バー)の立ち下がりでリセットされるプリセット・カウンタ143cと、1走査ライン分の表示データの転送に必要な高速クロックSCL(XSCL)の数をMPU10からセット可能なクロック数レジスタ143dと、プリセット・カウンタ1443cのキャリー出力CAを反転して間欠動作終了制御信号CA(バー)を作成するインバータ143fとを有する。

50 【0019】ダイレクト・メモル・アクセス(DMA)

₹,

回路150は、スタンバイ回路130からの一致信号 j により高速クロックSCLを用いて読み出しクロックR SKを専用バス14bに出力すると共にラインフラグレ ジスタ132に当該フラグアドレス信号及びフラグリセ ット信号を送るダイレクト・メモリ・アクセス (DM A)制御回路151と、読み出しクロックRSKによっ てVRAM12内の書換えアドレスの表示データを専用 バス14bを介して読み出しデータSDとして取込み、 その読み出しデータSDをシフトクロックSCLを用い てデータバス17のビット数又はフォーマットに変換し て得られた表示データDATA及びクロックSCLの周 波数と等しいシフトクロックXSCKをデータバス17 を介してXドライバ250-1~250-Nへ転送する データ変換回路152とを有している。

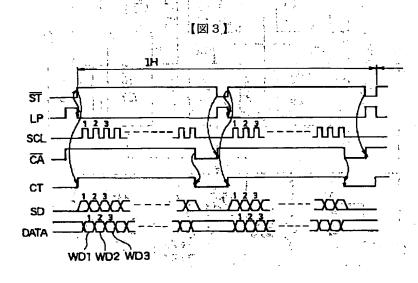

【0020】次に、モジュール・コントローラ100の 動作について図3を参照しつつ説明する。モジュール・ コントローラ100のうち、低周波発振回路110及び タイミング信号発生回路120は常時動作しているが、 Xドライバ250-1~250-Nが転送されて来る表 示データDATAを格納するフレームメモリ252-1 ~252-Nを有しているので、高周波発振回路140 は常時動作する必要がなく、後述するようにVRAM1 2内の表示データが変更された際に間欠動作する。低周 波発振回路110は低周波クロック fL を常時出力し、 タイミング信号発生回路120の分周器121は低周波 クロック f1 を所定の分周比で分周してラッチパルスL Pを生成する。ラッチパルスLPは1水平期間(1H) で2回発生し、その周波数は、640×480ドットの モノクローム表示の場合、最高32KHz~80KHz程度 である。垂直カウンタ122はラッチパルスLPを計数 30 して行アドレス信号RA及びフレーム開始パルスYDを 生成し、フレームカウンタ123はフレーム開始パルス YDを計数して液晶交流化信号FRを作成する。 このよ うに本例においては、LCDモジュール200側で必要 な低周波数のタイミング信号(ラッチパルスLP、走査 スタート信号YD及び液晶交流化信号FR)はタイミン グ信号発生回路120で作成される。

【0021】MPU10がVRAM12の表示データを リフレッシュ動作時に全体的に変更するときやフレーム 間引き方式で階調表示する際に部分的に変更するとき は、MPU10がシステムバス14及びインターフェー ス131を介してラインフラグレジスタ132の該当ア ドレスに転送指示フラグを立てる。一方、垂直カウンタ 122から行アドレス信号RAがラッチパルスLPの発 生の度に更新されているため、転送指示フラグの立った フラグアドレスと行アドレス信号RAが一致すると、比 較回路133から一致信号jが発生する。この一致信号 jは同期調整回路134へ入力され、図3に示すよう に、ラッチパルスLPの立ち下がりに同期し1水平期間 の周期の間欠動作開始制御信号ST(バー)が立ち上が 50

(6)

10

る。間欠動作開始制御信号ST(バー)が立ち上がる と、論理積ゲート141の出力には発振制御信号CTが 立ち上がり、CR発振部の初段の論理積ゲート142a の一方入力は高レベルとなるので、CR発振部は抵抗選 択スイッチSW1 ~ SW1 の開閉組合わせで指定された 帰還時定数に応じた高周波数で発振クロックfH を発生 し始める。発振クロックfHはインバータ143a,論 理積ゲート143b及びインバータ134eを介してプ リセット・カウンタ143cに供給されと共に、論理積 ゲート144からクロックSCLとして出力される。こ 10 のクロックSCLは高周波クロックであり、DMA回路 150の表示データの読込み及び転送に利用される。プ リセット・カウンタ143cは間欠動作開始制御信号S T(バー)の立ち下がりでリセットされ、キャリー出力 CAは低レベルになるが、カウント値がクロック数レジ スタ143dで指定されたクロック数に達すると、高レ ベルのキャリー出力CAを出し、その反転信号たる間欠 動作終了制御信号CA(バー)が図3に示すように立ち 下がる。間欠動作終了制御信号CA(バー)が立ち下が ると、発振制御信号CTも立ち下がり、これにより可変 20 周波数CR発振器142の発振動作が中止される。この ように、可変周波数CR発振器142は間欠動作開始制 御信号ST(バー)と間欠動作終了制御信号CA(バ ー)で始点及び終点が限定された期間だけ間欠的に発振 動作し、クロック数レジスタ143dで指定される1走 査ライン分の表示データの転送に必要なクロック数の高

国シインガの扱示が、シの転送に必要なシェンシン (1) 周波クロック f<sub>H</sub> を発生する。これによって、表示デー タの変更がないときは可変周波数CR発振器142の不 必要な発振動作を解消することができ、消費電力の削減 に寄与することになる。

【0022】他方、DMA回路150において、スタン バイ回路130の比較回路133から一致信号jが出力 されると、DMA制御回路151は高速クロックSCL を用いて読み出しクロックRSKを専用バス14bに出 力する。これによりVRAM12内の書換えアドレスの 表示データ(新データ)が図3に示すように読み出しデ ータSDとしてデータ変換回路152に取り込まれる。 取り込まれた読み出しデータSDはデータバス17のビ ット数又はフォーマットに変換され、表示データDAT

AとクロックSCKの周波数に等しいシフトクロックX SCKがデータバス17を介してXドライバ250-1 ~250-Nへ転送される。また、DMA制御回路15 1はラインフラグレジスタ132に当該フラグアドレス 信号及びフラグリセット信号を送る。これによりデータ 変換回路152に取り込まれて転送された表示データの フラグアドレス内の転送指示フラグが倒される。そして 次の行アドレス信号RAが発生すると、次の高速クロッ クSCKによって上記の動作が繰り返され、1水平期間 で2走査ライン分の表示データDATAの転送が完了す

50、1走査ライン分の表示データDATAが転送される

(7)

と、キャリー信号の反転信号CA(バー)が低レベルと なるため、転送動作が一時中止される。しかし、Xドラ イバ250-1~250-Nにはフレームメモリ252 -1~252-Nが転送データを格納しているため、シ フトクロックXSCLの動作・停止を1走査ライン毎に 制御しても、表示に影響を及ぼすことはない。

11

【0023】このように、Xドライバ250-1~25 0-Nにフレームメモリ252-1~252-Nを内蔵 させて高周波発振回路140を間欠動作させるモジュー ル・コントローラ110を構築したことにより、VRA M12の表示データの変更があったときのみ走査ライン 毎の表示データをフレームメモリ252-1~252-Nへ転送させることができる。このため、高周波発振回 路140の常時動作が無くなるので、表示データの変更 がなければ大幅な消費電力の削減が可能となる。また、 このような間欠制御は既に公知であるフレーム間引き方 式の階調表示を行う場合や、画面に対する動画表示面積 の少ない表示を行う場合にも対応でき、従来表示システ ムとの互換性も良好である。なお、上記モジュール・コ ントローラ100の高周波発振回路140は、可変周波 数CR発振器142を用いて構成されているが、これに 限らず、ラッチパルスLPに同期して高周波クロックを 発生する位相同期回路(PLL)を用いることができ る。かかる場合、高周波クロックは位相同期回路の電圧 制御発振器の出力から取り出すようにする。更に、高周 波発振回路140はモジュール・コントローラ100に 内蔵させずに、外部の高周波クロック源から供給される ようにも構成できる。或いはモジュール・コントローラ 100は、ホストMPU10又はVRAM12と同一の 半導体集積回路上に構成すれば、接続配線を減らすこと ができる。

【0024】 〔複数ライン同時選択駆動方法の説明〕次 に、Xドライバ(信号電極駆動回路)250の構成及び 動作についての説明に移るが、本例の単純マトリクス型 液晶表示装置は、従来の電圧平均化法による液晶素子駆 動方法でなく、複数走査電極を同時に選択するいわゆる 複数ライン同時選択(Multiple Lines Selection) 駆動 方法の改良技術に基づくものであるため、Xドライバ等 の構成の理解を容易にするべく本発明が基にしている複 数ライン同時選択の原理を先ず説明しておく。

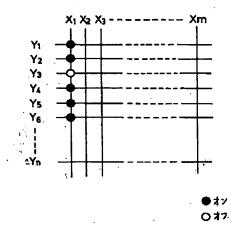

【0025】電圧平均化法によるマルチプレクス駆動方 法は、図4に示すような単純マトリクス型の液晶素子等 を駆動する場合、一般に走査電極 $Y_1, Y_2 \cdots Y_n & 1 ラ$ インずつ順次選択して走査電圧を印加すると共に、その 選択される走査電極上の各画素がホンかオフかによっ て、それに応じた信号電極波形を各信号電極 $X_1, X_2 \cdots$  $X_m$  に印加することで液晶素子等を駆動するものであ る。図5はそのときの印加電圧波形の一例を示すもの で、同図(a), (b)はそれぞれ走査電極 $Y_1, Y_2$ に 12

印加する電圧波形、同図(c)は信号電極X1に印加す る電圧波形、同図(d)は走査電極Y1と信号電極X1 との交差する画素に印加される合成電圧波形を示す。 【0026】ところで、上記のように走査電極を1ライ ンずつ順次選択して駆動する方法では、駆動電圧が比較 的高い。また図6に示すようにオフ状態においてもやや 高い電圧がかかると共に、オン状態では電圧の減衰が大 きいため、コントラストが悪い。更に、フレーム階調を 行うとフリッカーが大きい等の不具合がある。

10 【0027】そこで、コントラストを改善し、フリッカ ーを抑制するために、順次複数本の走査電極をまとめ同 時に選択して駆動するいわゆる複数ライン同時選択(Mu ltiple Lines Selection) 駆動方法が提案されている (例えば、A GENERALI2DADDERESSING TECHNIQUE FORRMS RESPONDING MATRIX LCDS. 1988 INTERNATIONALDISPLAY RESERCH COMFERENCE P80 ~85参照)。

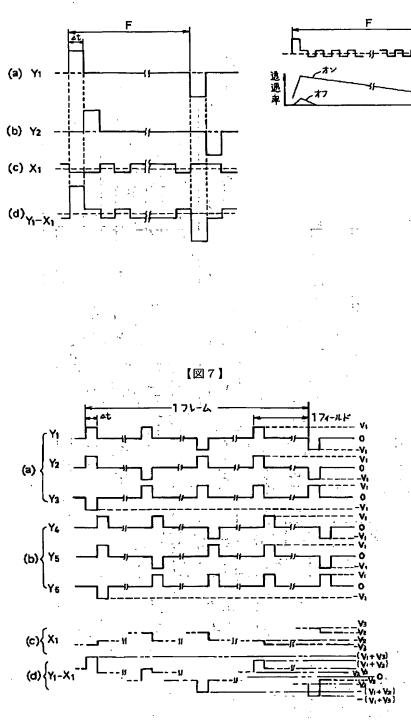

【0028】図7は上記の複数ライン同時選択駆動方法 によって液晶素子を駆動する場合の印加電圧波形の一例 を示すものである。本例は走査電極を順次3本ずつ同時

- 20 に選択して駆動するもので、例えば図4に示すような画 素表示を行う場合には、最初に3本の走査電極Y1, Y

2, Y3 を同時選択して、それらの走査電極Y1,

- $Y_2$ ,  $Y_3$ に、それぞれ例えば図7の(a)に示すよう な走査電圧を印加する。

- 【0029】次いで図4において走査電極Y4,Y5,Y6 を選択して、それらの走査電極Y4,Y5,Y6 に例えば図 7の(b)のような走査電圧パターンを印加するもの で、このような同時選択を全ての走査電極Y1,Y2 …Y nについて順次行う。更に次のフレームでは電位を逆転 し、液晶の交流化駆動を行なう。

【0030】従来の電圧平均化法では1フレーム期間に 1回1走査電極を選択していたが、複数ライン同時選択 では、走査選択方法の正規直交性を保ちながら選択期間 を時間的に1フレーム内に均等分散し、これと同時に、 走査電極を特定本数の組(ブロック)にして選択し、空 間的に分散したものである。ここで、「正規」とは、す べての走査電圧がフレーム周期単位で同一の実効電圧値 (振幅値)を持つことを意味する。また「直交」とは、

ある走査電極に与えられる電圧振幅が他の任意の走査電 極に与えられる電圧振幅を1選択期間毎に積和したとき フレーム周期単位では0になることを意味する。この正

規直交性は、単純マトリクス型LCDにおいては各画素 を独立してオン・オフ制御するための大前提である。例 えば、図7の例では、選択時の $V_1$ レベルを「1」, –  $V_1$ レベルを「-1」としたときの1フレーム分の行列 式F<sub>3</sub>を、非選択期間は0であるので省略して表記する と、

- T ( 0 0 3 1 )

- 【数1】

30

40

$$F_{3} = \begin{pmatrix} 13 & & & & & & \\ 1 & 1 & -1 & 1 & \\ 1 & -1 & 1 & 1 & \\ -1 & 1 & 1 & 1 \end{pmatrix} = (f_{ij}) \cdots (1)$$

(8)

【0032】である。例えば第1行目(Y<sub>1</sub>)と第2行 \*【0033】 目(Y<sub>2</sub>)の直交性は、 \* 【数2】

$$\sum_{i=1}^{4} f_{1,i} \times f_{2,i} = 1 + (-1) + (-1) + 1 = 0$$

【0034】と検証される。直交性については、数学的 な内容になるので詳細な説明は割愛するが、液晶を駆動 する場合、低周波成分はフリッカーの原因になるので、 h本同時選択するとき直交性の保たれる必要最小限の行 列を選択する必要がある。一般にh本同時選択する場 合、上記行列式(1)の列数に相当する1フレーム内の 必要最少分散選択数は、nを自然数とするとき、 $2^{n-1}$ <h $\leq 2^{n}$ を満足する $2^{n}$ の値となる。例えば、図8に 示す3本同時選択の場合の必要最少限の分散選択数は4 となる。またh= $2^{n}$ のときは、1選択期間 $\Delta$ tは、電 圧平均化法での1選択時間(1H)に等しい。 【0035】一方、信号側電圧波形は、レベル数(h+ 1)の離散的な電圧レベルの中から1つのレベルを表示

データに応じて決められる。電圧平均化法では、図5に※

$$C = \sum_{i=1}^{\infty} (f_{ii} \oplus S_{ii})$$

【0037】但し、(1)式でf<sub>i1</sub>が「1」であるとこ ろは、式(3)では「0」として扱う。 【0038】ここで、C値は0からhまでの値をとる。 電圧平均化法の場合は、h=1であるので、C値は0か

ら1である。図7の例では、列パターン(1,1,1)★30

10※示すように、1行選択波形に対して信号電極(行)波形は、1対1に対応しているため、オンかオフかに対応する2つの電圧レベルのうちから1つのレベルを出力するものであった。図7に示すようなh本同時選択の場合は、h本組になった行選択波形に対して等価的なオン・オフ電圧レベルを出力する必要がある。この等価的なオン・オフ電圧レベルは、オン表示データを「1」、オフ表示データを「0」としたとき、信号電極側データパターン(S1j, S2j, …, Shj)と上記行列式の列パターン(走査電極選択パターン)との不一致数Cで決められ20 る。

【0036】 【数3】

... (3)

... (2)

★の場合を考えると、信号電極側データパターン及びXド ライバ出力電位は、表1のようになる。

【0039】 【表1】

| 不一致数                      | 信号電極データパターン |           |         | データバターン数 | XFライバ出力電位      |

|---------------------------|-------------|-----------|---------|----------|----------------|

| C = 0                     | (1, 1, 1)   |           | ·       | 1        | - V 3          |

| $C \stackrel{\cdot}{=} 1$ | (0,1,1)     | (1,0,1)   | (1,1,0) | 3        | — V 2          |

| C = 2                     | (1,0,0)     | (0, 1, 0) | (0,0,1) | 3        | V 2            |

| C = 3                     | (0,0,0)     |           |         | · 1      | V <sub>a</sub> |

40

【0040】表1に示す各不一致数に対するデータパタ ーン数は、どの列に対しても同じである。従って、列パ ターンが決まっていれば、Xドライバの出力電位は、不 ー致数又は信号電極データパターンから直接Xドライバ 出力電位をデュードして決めることができる。具体的に は、図7(c)に示す信号電極電圧波形となる。図4に おける信号電極X1と走査電極Y1,Y2,Y3との交差画 素の表示は、順に1(オン),1,0(オフ)で、これ に対する最初の $\Delta$ t内の走査電極の電位値は、順に1

(V<sub>1</sub>), 1, 0 (−V<sub>1</sub>) である。従って、不一致数

は0であるから、信号電極X<sub>1</sub>の最初のΔt内の出力電 <sup>50</sup>

位は表1から-V3 である。以下同様にして信号電極の 出力電位波形が各画素に印加される。なお、図7の

(d)は、走査電極Y1と信号電極X1とが交差する画 素に印加される電圧波形、即ち、走査電極Y1に印加さ れる電圧波形と信号電極X1に印加される電圧波形との 合成波形である。

【0041】上記のように、順次複数本の走査電極を同時に選択して駆動する手法は、図5に示す従来の1ラインずつ選択して駆動する方法と同じオン/オフ比を実現した上で、Xドライバ側の駆動電圧を低く抑えることができる利点がある。例えば、液晶のしきい値VTHを2.

1 V, デューティー比1/240では、Xドライバの最 大駆動電圧振幅は8 V程度である。これはXドライバを 高耐圧集積回路として構成する必要がなく、従来法より 微細な半導体製造プロセスをそのまま適用できる途を開 き、Xドライバ内蔵RAMのビット数を経済的に増やす ことができることに繋がる。

【0042】本出願人は、上記の複数ライン同時選択駆動方法についても特願平4-143482号を以て既に開示してある。この均等分散型複数ライン同時選択駆動方法では、マトリクス型表示装置において、順次複数本の走査電極を同時に選択し、かつその選択期間を1フレームの中で複数回に分けて電圧を印加する駆動回路を設けたことに特徴を有する。即ち、1フレーム中に1回

(まとめてh Δ t の期間) 選択するのではなく、その選 択期間を1フレーム中で複数回に分けて電圧を印加する ように駆動することによって、1フレーム中で或る画素 には複数回電圧が印加されることになるので、明るさが 維持されコントラストの低下を抑制することができる、 特に、累積応答効果の少ない高速応答性の液晶パネルの 使用に有意義となる。

【0043】この事については、図8に示すように非選 択期間(ある走査電極が選択されてから次に選択される までの期間)が短くなり、従来例における図6との比較 からも明らかなように、オン状態はより明るく、かつオ フ状態はより暗くなってコントラストを高めることがで きる。またフリッカーも減少させることができる。この ように、改良された複数ライン同時選択駆動方法は、走 査電極の複数のパルスパターンを一括して出力するので はなく、分散して出力するものである。なお、本例にお いては各選択期間の選択パルスを出す順番は任意であ り、1フレームの中で適宜入れ替えることができる。ま た本例では4つの列パターンを1つずつ4回に分けた が、複数ずつ、例えば2つずつ2回に分けて出力するこ ともできる。

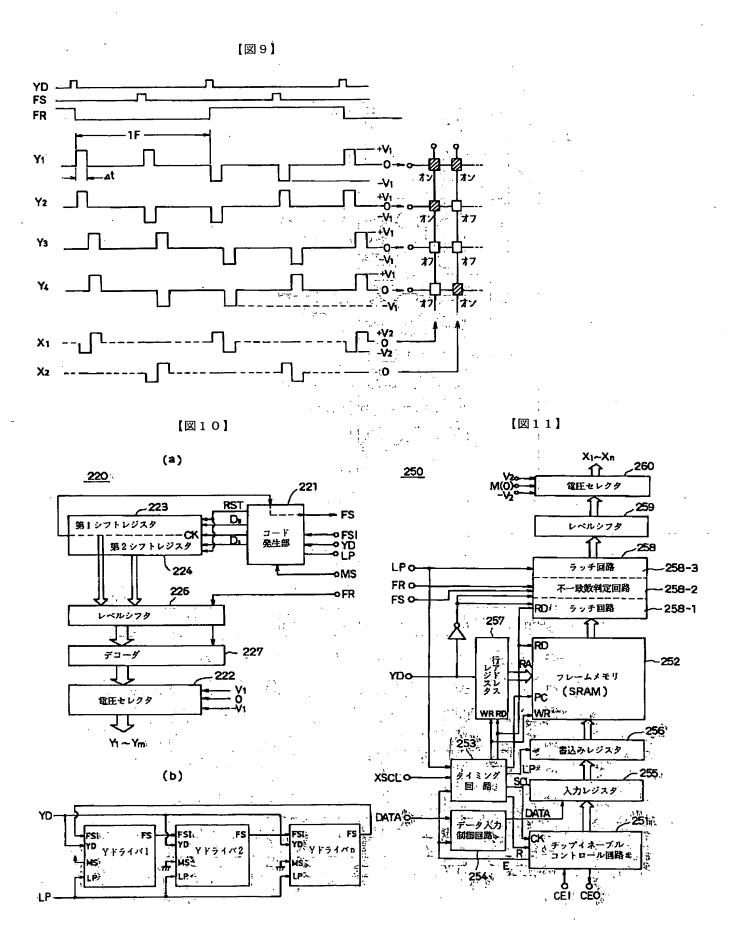

【0044】ここで、複数ライン同時選択駆動方法の説 明に深入りせずに、ドライバの説明に話しを戻すことに する。ただ、上述したように本例の液晶表示装置は均等 分散型複数ライン同時選択駆動方法を採用しており、ま たドライバがフレームメモリ内蔵型でありながらモジュ ール・コントローラ100によって制御されるようにな っているので、以下の説明では、ドライバが両者の要請 に叶う構成でなければならないことを理解されたい。 【0045】 [走査電極駆動回路(Yドライバ)の説 明]ここで、以下に説明するドライバの複数ライン同時

選択駆動方法において、同時選択にあずかる走査電極の 数は、回路部の機能を容易に理解するために、最小の本 数即ち2本(h=2)とする。従って、図9に示すよう に、21 = 2の数だけ走査電極波形の列パターンがあ る。また2つの異なる電圧パルスパターンを連続した2 本の走査電極に印加するようにしてあり、1フレームは 50 選択駆動方法において、同時選択にあずかる走査電極の その低論理振幅レベルから高論理振幅レベルへ変換された る。レベルシフタ226から出力される高論理振幅レベ ルの電圧選択コードD<sub>0</sub>, D<sub>1</sub>, は同時にレベル変換された 液晶交流化信号F.Rと共に波形形成部としてのデコーダ 227に供給され、選択制御信号が生成される。この選

(9)

16

$2 7 - \mu k$  (2 垂直走査)により構成される。走査電極の総数を120本とすると、同時選択される2本の走 査電極のブロックの数は60である。そして、あるブロ ックに対しては、最初に2種類のパルスパターンが印加 されてから次の異なる2種類のパルスパターンが印加さ れるまでには(60-1)  $\Delta t = 59 \Delta t$ の非選択期間 がある。17レームは120 $\Delta t$ で完了する。但し、 $\Delta$ tは1選択期間(1水平期間)である。

【0046】Yドライバ220は、図10に示すよう に、フレーム開始パルスYDやラッチパルス等を基にフ

- 10 に、 クレ エ (所知) ルス1 D、 (クノ) ルルス4 と 温に j  $\gamma - \mu$  ) ド毎の列パターンを作成するコード発生部221 を有する半導体集積回路である。本例の走査電極Y1 ~ Y<sub>n</sub> の印加電圧は、選択期間においてはV1 又は $-V_1$ であり、非選択期間においては0 Vで、合計3 レベルあ るので、電圧セレクタ222に対する選択制御情報は各 走査電極Y1 ~ Y<sub>n</sub> 毎2ビットが必要である。このた め、複数ライン同時選択のためのコード発生部221 は、フィールド計数カウンタ(図示せず)と第1及び第 2シフトレジスタ223、224をフレーム開始パルス

- 20 YDで初期化した後、第1フィールドの選択列パターン に対応する2ビットの電圧選択コードD0,D1を直並列 変換用の第1シフトレジスタ223及び第2シフトレジ スタ224に転送する。第1シフトレジスタ223及び 第2シフトレジスタ224はそれぞれ走査電極の本数に 対応した120ビットシフトレジスタであり、第1シフ トレジスタ223は下位ビットの電圧選択コードD 0,を、第2シフトレジスタ224は上位ビットの電圧選 択コードD1をそれぞれ同一のシフトクロックCKによ り格納する。シフトクロックCKはラッチパルスLPを

- 30 1/2分周したもので、コード発生部221のタイミン グ生成回路(図示せず)により発生する。コード発生部 221はラッチパルスの2クロック目から第1フィール ド終了までの期間は、非選択パターンに対応するコード を発生する。シフトレジスタはシフトクロックCKに対 して単一の240ビットのシフトレジスタがあるのでは なく、シフトクロックCKに対して並列の120ビット のシフトレジスタ223、224が設けられているの で、ラッチパルスLPにより低い周波数で動作させるこ とができ、極めて低消費電力動作が可能となっている。

- 40 【0047】第1シフトレジスタ223及び第2シフトレジスタ224の各ビットの電圧選択コードD0,D

1は、シフトクロックCKの発生を契機に隣接ビットにシフトされ、選択時間Δtだけ出力維持される。このシフトレジスタの出力はレベルシフタ226へ供給され、その低論理振幅レベルから高論理振幅レベルへ変換される。レベルシフタ226から出力される高論理振幅レベルの電圧選択コードD0,D1,は同時にレベル変換された液晶交流化信号FRと共に波形形成部としてのデコーダ。227に供給され、選択制御信号が生成される。この選ジ報制御信号で電圧セレクタ222が開閉制御されること

17

により各走査電極 $Y_1 \sim Y_n$  へ印加電 $EV_1$ , 0, -V1 のいずれかが供給される。

【0048】本例では、図10(b)に示すように、複 数のYドライバ1~nをカスケード接続できるようにコ ード発生部221の機能を初段Yドライバ1と次段以降 のYドライバ2~nとでセレクト端子MSを使って変え ることを前提としている。即ち、初段Yドライバ1で は、前述のフレーム開始パルスYDによる初期化後、前 述の2つのシフトレジスタ223, 224に向けて電圧 選択コードを発生するタイミングに移るが、次段以降 は、セレクト端子MSが低レベル入力になっているた め、電圧選択コードを発生するタイミングには自動的に 移らない。次段以降のYドライバ2~nは、初段のキャ リー信号(FS)をFSI入力端子から入力して初めて 電圧選択コードを前述の2つのレジスタ223,224 に向けて発生する。そして最終段のYドライバnからの キャリー信号(FS)が出力されたときが、第1フィー ルドが終了するときである。このときはコントローラか らは第2フィールドの開始信号は来ないので、最終段の Yドライバnのキャリー信号(FS)を初段のYドライ バ1のFSI端子及びXドライバのFS端子に帰還し、 第2フィールドの電圧選択コードを前述の2つのシフト レジスタ223、224に対して発生する。この後、前 述した第1フィールドと同様に動作し、第2フィールド を終了し、次のフィールド(第1フィールド)の動作に 移る。以上の機能は、コントローラに対する同時選択ラ イン数やYドライバの端子数の制約を緩和し、従来の電 圧平均化法の場合と同じ周波数のフレーム開始パルスY D, ラッチパルスLPを使うことができる。

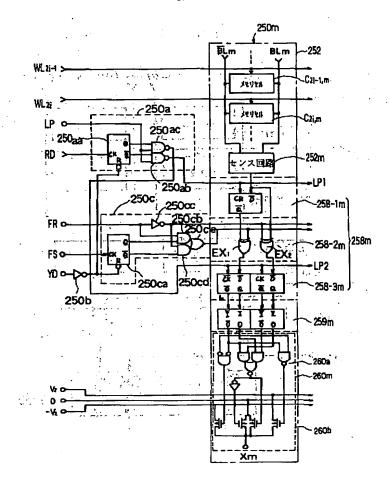

【0049】〔信号電極駆動回路(Xドライバ)の説 明〕複数のXドライバ250-1~250-Nは共に同 ー構成の半導体集積回路で、これらは図1に示すように 相互にチップイネーブル出力CEOとチップイネーブル 入力CEIを介してカスケード接続されている。いずれ のXドライバ250も、従来のRAM内蔵型ドライバと 異なり、MPU10に直結するシステムバス14を共有 せず、データバス17を介してモジュール・コントロー ラ100に繋がっているだけである。各Xドライバ25 0は、図11に示すように、アクティブ・ローの自動パ ワーセーブ回路としてのチップイネーブル・コントロー ル回路251と、主にモジュール・コントローラ100 から供給される信号を基に所要のタイミング信号等を形 成するタイミング回路253と、イネーブル信号Eの発 生を契機にモジュール・コントローラ100から転送さ れる表示データDATAを取り込むデータ入力制御回路 254と、表示データDATA(1ビット、4ビット又 は8ビット)をシフトクロックXSCLの立ち下がる度 に順次取り込み1走査ライン分の表示データDATAを 格納する入力レジスタ255と、入力レジスタ255か らの1走査ライン分の表示データDATAをラッチパル 50

スLPの立ち下がりにより一括ラッチして1シフトクロ ックXSCL以上の書込み時間をかけてフレームメモリ (SRAM) 252のメモリマトリクスに書き込む書込 みレジスタ256と、走査スタート信号YDにより初期 化され書込み制御信号WR又は読み出し制御信号RDの 印加の度にフレームメモリ252の行(ワード線)を順 次選択する行アドレスレジスタ257と、フレームメモ リ252よりの表示データと走査電極の列パターンとの 組から対応する信号電極の駆動電圧情報を割り出す信号 パルス割り出し回路258と、信号パルス割り出し回路 258からの低論理振幅レベルの信号を高論理振幅レベ

ルの信号に変換するレベルシフタ259と、レベルシフ タ259から出力される高論理振幅レベルの電圧選択コ ード信号により電圧 $V_2$ , M(例えば0),  $-V_2$ のい ずれかを選択して各信号電極 $X_1 \sim X_n$ に印加する電圧 セレクタ260とを有している。

【0050】ドライバチップ単位のパワーセーブを行な うチップイネーブルコントロール回路251とそれに関 係する回路部分は従来技術を使用できる。チップイネー ブルコントロール回路251は、チップイネーブルにな っているチップだけがシフトクロックXSCLと表示デ ータDATAをドライバ内に取り込むように内部イネー ブル信号を発生し、タイミング回路253とデータ入力 制御回路254の動作/停止を制御する。この制御は、 ラッチパルスLPの周期毎に繰り返される。即ち、ラッ チパルスLPの入力によりチップイネーブルコントロー ル回路251の内部は、カスケードされたどのドライバ チップもパワーセーブ状態からスタンバイ状態になると 共に、イネーブル出力CEOは高レベルになる。ここ

で、どのドライバチップがイネーブルになるかパワーセ 30 ーブ状態を保つかは、イネーブル入力端子CEIの状態 によって決定される。即ち、図1の例では、初段のXド ライバ250-1のチップイネーブル入力CEIは、接 地(アクティブ)されているので、即座に内部イネーブ ル信号Eはアクティブ状態になり、シフトクロックXS CL、表示データDATAを内部に取り込む。チップイ ネーブルコントロール回路251は、入力レジスタ25 5のビット数分の表示データを取り込に必要なシフトク ロック数分のシフトクロックを入力した時点でイネーブ 40 ル出力CEOを高レベルから低レベルにする。これによ ってカスケード接続された次段Xドライバ250-2の イネーブル入力CEIは低レベルとなり、即座に次段ド ライバの内部イネーブルEはアクティブとなる。これ以 降の動作は前述の初段ドライバの動作と同じである。以 下同様に3段目以降のXドライバ250-3~250-Nのチップイネーブル入力CEIは順次低レベルとな り、所定の入力レジスタ255に対する表示データが取 り込まれる。従って、N個のXドライバをカスケード接 続しても、表示データの取り込み動作をするXドライバ は、常時1個に限られるので、表示データの取り込み動

(11)

19 作に係わる消費電力を低く抑えることができる。

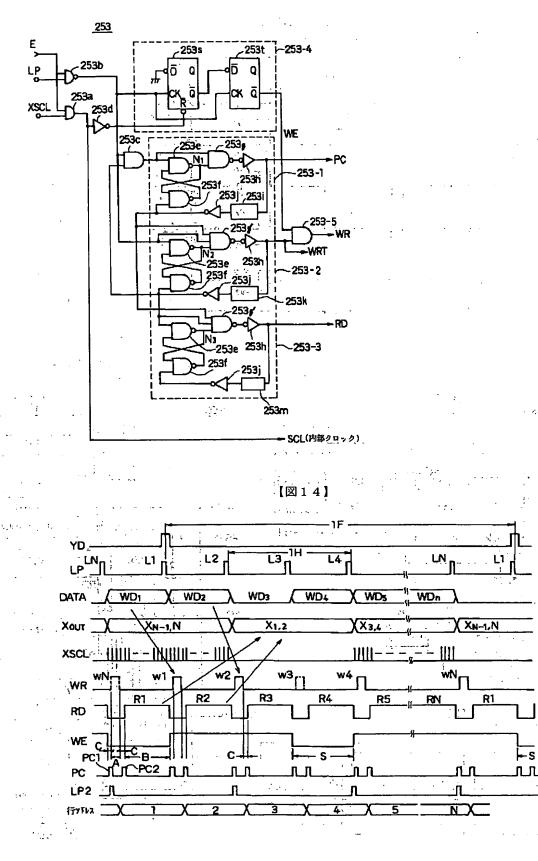

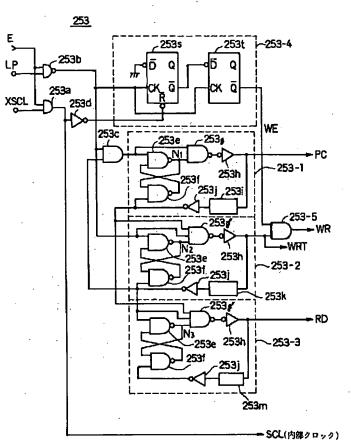

> 【0051】タイミング回路253の構成の詳細は、一 部省略して示す図12のように、上記シフトクロックX SCLをイネーブル信号Eの応答により内部へ取り込む ための論理積ゲート253aと、イネーブル信号Eの応 答によりNANDゲート253bを介して内部へ取り込 んだラッチパルスLP及び書込み制御信号WRの遅延し た反転パルスに基づき1ラッチパルスの周期内にプリチ ャージ用の2発の準備パルスを生成する論理積ゲート2 53cと、この論理積ゲート253cの出力パルスの立 ち上がりにトリガして所定パルス幅のプリチャージ制御 信号PCを発生する第1のワンショット・マルチバイブ レータ(プリチャージ制御信号発生回路)253-1 と、これにカスケード接続され、プリチャージ制御信号 PCの遅延した反転パルス及びラッチパルスLPの反転 パルスの立ち上がりにトリガして所定パルス幅の書込み 制御信号WRを生成する第2のワンショット・マルチバ イブレータ(書込み制御信号発生回路)253-2と、 これにカスケード接続され、プリチャージ制御信号PC の遅延した反転パルス及び書込み制御信号WRの遅延し た反転パルスの立ち上がりにトリガして所定パルス幅の 読み出し制御信号RDを生成する第3のワンショット・ マルチバイブレータ(読み出し制御信号発生回路) 25 3-3と、シフトクロックXSCLのインバータ253 dを介した逆相クロックでリセットされシフトクロック XSCLの入来を検出するシフトクロック検出回路25 3-4と、シフトクロック検出回路253-4からのシ フトクロック検出信号WEにより第2のワンショット・ マルチバイブレータ253-2からの書込み制御信号W Rを通過・遮断する書込み禁止用論理積ゲート253-5とを有している。

【0052】第1のワンショット・マルチバイブレータ 253-1は、論理積ゲート253cの出力の立ち下が りによりノードN1 を高レベルにセットするNANDゲ ート253e, 253fから成るフリップ・フロップ と、ノードN1 が高レベルのとき高レベルのプリチャー ジ制御信号PCを作成するNANDゲート253g及び インバータ253hと、フレームメモリ252内の回路 での等価的な信号遅延時間を見越して作り込まれプリチ ャージ制御信号 PCを遅延する遅延回路253 iと、そ のプリチャージ制御信号PCを反転してNANDゲート 253fのリセット入力に加えるインバータ253jと を有している。第1のワンショット・マルチバイブレー タ253-1においては、NANDゲート253eのセ ット入力端子の入力が立ち下がるとノードN1 は高レベ ルにセットされ、次いでANDゲート253cの出力が 高レベルになったときプリチャージ制御信号PCが立ち 上がり、しかる後遅延回路253iで決まる遅延時間が… 経過すると、NANDゲート 2:5 3 f のリセット入力が 立ち下がり、ノードN1 は低レベルとなるので、プリチ 50 20

ャージ制御信号 PCが立ち下がる。論理積ゲート253 cの出力の立ち上がりは、ラッチパルス L Pの立ち上が り時と後述する書込み制御信号WRの遅延信号の立ち上 がり時に発生するので、1 ラッチパルスの周期内でプリ チャージ制御信号 PCのパルスは2回発生する。

【0053】第2及び第3のワンショット・マルチバイ ブレータ253-2,253-3も第1のワンショット ・マルチバイブレータ253-1とほぼ同様な回路構成 を有しているので、同一構成の部分には図12では同一

- 参照符号で示してある。第2のワンショット・マルチバ 10 イブレータ253-2は、プリチャージ制御信号PCの 遅延反転信号、ラッチパルスLPの反転信号及びNAN Dゲート253eのノードN2を3入力とするNAND ゲート253g′とフレームメモリ252内の回路での 等価的な信号遅延時間を見越して作り込まれ書込み制御 信号WRを遅延する遅延回路253kを有している。N ANDゲート253eのノードN2 はラッチパルスLP の反転信号の立ち下がりで高レベルにセットされるが、 プリチャージ制御信号PCの最初の立ち下がり(プリチ

- ャージ制御信号PCの遅延反転信号の最初の立ち上が 20 り)によりNANDゲート253g'の出力が立ち下が るので、書込み制御信号WRが立ち上がり、しかる後遅 延回路253kで決まる遅延時間が経過すると、NAN Dゲート253fのリセット入力が立ち下がり、ノード N2 は低レベルとなるので、書込み制御信号WRが立ち 下がる。この後、2発目のプリチャージ信号PCの遅延 反転信号が立ち上がるが、ノードN2 は未だラッチパル スLPの立ち下がりによって高レベルにはセットされて いないので、NANDゲート253g'の出力は高レベ

- ルのままであり、1ラッチパルスの周期内においては、 書込み制御信号WRのパルスは最初のプリチャージ制御 信号の立ち下がりにより1パルス出力されるのみであ る。第3のワンショット・マルチバイブレータ253-3は、プリチャージ制御信号 PCの遅延反転信号,書込 み制御信号WRの遅延反転信号、NANDゲート253 eのノードN3 を3入力とするNANDゲート253 g'と、フレームメモリ252内の回路での等価的な信 号遅延時間を見越して作り込まれ読み出し制御信号RD を遅延する遅延回路253mを有している。NANDゲ ート253eのノードN3は、プリチャージ制御信号P 40 Cの最初の立ち下がり(プリチャージ制御信号PCの遅 : 延反転信号の最初の立ち上がり)の後に発生する書込み 制御信号WRの遅延反転信号の立ち下がり(書込み制御 信号WRの立ち上がり)で高レベルにセットされている、 ので、2発目のプリチャージ制御信号 P C の最初の立ち; 下がり(プリチャージ信号PCの遅延反転信号の最初の 立ち上がり)によりNANDゲート253.g'の出力が 立ち下がり、読み出し制御信号RDが立ち上がることな る。しかる後遅延回路253mで決まる遅延時間が経過。 すると、NANDゲート2531のリセット入力が立ち

下がり、ノードN3 は低レベルとなるので、読み出し制 御信号RDが立ち下がる。1ラッチパルスの周期内にお いては、読み出し制御信号RDは2発目のプリチャージ 制御信号PCの立ち下がりにより所定パルス幅の1パル ス出力されるのみである。

【0054】シフトクロック検出回路253-4は、シ フトクロックXSCLの逆相クロックをリセット入力R (バー)とすると共に、ラッチパルスLPの反転クロッ クの立ち上がりで接地電位(低レベル)をデータ反転入 カD(バー)として記憶するD型フリップ・フロップ2 53sと、ラッチパルスLPの反転クロックの立ち上が りでD型フリップ・フロップ253sの反転出力Q(バ ー)をデータ反転入力D(バー)として記憶するD型フ リップ・フロップ253tを有している。シフトクロッ クXSCLの入来があると、まず最初のシフトクロック XSCLのパルスでD型フリップ・フロップ253sが リセットされ、そのQ(バー)出力が高レベルとなって いるが、ラッチパルスLPの立ち下がりによってD型フ リップ・フロップ253sには接地電位がデータ反転入 カD(バー)として記憶されるのでそのQ(バー)出力 20 が低レベルへ遷移すると共に、D型フリップ・フロップ 253tは高レベルのデータ反転入力D(バー)を記憶 するので、そのQ(バー)出力たるシフトクロック検出 信号WEが高レベルとなる。2発目のシフトクロックX SCLの入来すると、D型フリップ・フロップ253s はリセットされ、そのQ(バー)出力が高レベルに戻 る。このようにシフトクロックXSCLの入来が続く限 り、D型フリップ・フロップ253tからのシフトクロ ック検出信号WEは高レベルであるので、論理積ゲート 253-5は導通状態のままであり、第2のワンショッ ト・マルチバイブレータ253-2からの書込み制御信 号WRはフレームメモリ等へ出力され続ける。他方、シ フトクロックXSCLの入来が止み、最後のシフトクロ ックXSCLのパルスでD型フリップ・フロップ253 sのQ(バー)出力が低レベルに設定された状態のまま でラッチパルスLPが入来すると、D型フリップ・フロ ップ253tからのシフトクロック検出信号WEが低レ ベルになるので、論理ゲート253-5が閉じ、書込み 制御信号WRの通過が禁止される。

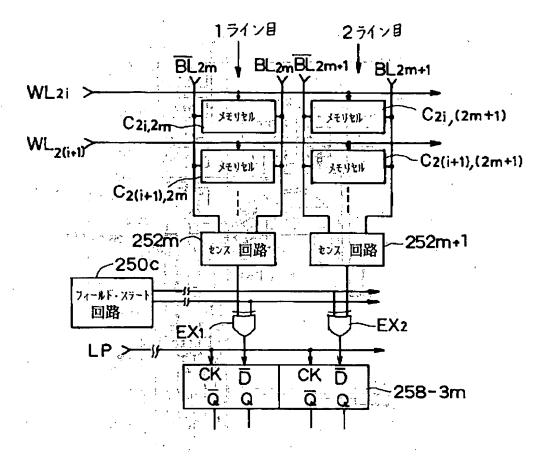

【0055】次に、図13を参照しつつXドライバ25 Oにおける周辺回路とフレームメモリ252から信号パ ルス割り出し回路258,レベルシフタ259及び電圧 セレクタ260までの1信号電極当り(1出力X<sub>m</sub>)の mビット回路部250mに着目した回路構成を説明す る。フレームメモリ252のメモリマトリクスにおける 奇数ワード線W<sub>2i</sub>-1,偶数ワード線W<sub>i</sub>とビット線BL m,BL<sub>m</sub>(バー)との交点にはメモリセルC<sub>2i</sub>-1,m、 C<sub>2i,m</sub>があり、画素P<sub>2i</sub>-1,m、P<sub>2i,m</sub>に対応した表 示データ(オン・オフ情報)が格納されている。ラッチ パルスLPが発生すると、タイミング回路253からプ 22

リチャージ信号PC,書込み制御信号WR又は読み出し 制御信号RDが生成されるので、フレームメモリ252 への印加により奇数ワード線W2i-1が行アドレスレジス タ257の順次的な指定によりフレームメモリ252内 の行アドレスデコーダによって選択され、メモリセルC 2i-1,mについての書込み又は読み出しが行われる。また 次のラッチパルスLPが発生すると、偶数ワード線Wi が選択され、メモリセルC2i,mについての書込み又は読 み出しが行われる。なお、読み出し動作においては読み

10 出し制御信号RDによりセンス回路252mが能動化さ れ、メモリセルから表示データが出力される。

【0056】本例のXドライバ250においては、前述 したような2 ライン同時選択駆動方式を採用している都 合上、1水平期間毎2ラインに亘る表示データと走査電 極の列パターンとから信号電極電位を決定する必要があ る。周辺回路には偶奇ライン識別回路(同時選択ライン のライン順番識別回路) 250 a が設けられており、こ の偶奇ライン識別回路250aは、フレーム開始パルス YDのインバータ250bを介した逆相パルスによって リセットされ読み出し制御信号RDの入来毎に記憶内容 の反転するD型フリップ・フロップ250aaと、その Q(バー)出力とラッチパルスLPとを2入力とする奇 数ライン検出用NANDゲート250abと、D型フリ ップ・フロップ250aaのQ出力とラッチパルスLP とを2入力とする偶数ライン検出用NANDゲート25 Oacとから構成されている。奇数番目のラッチパルス LPが立ち上がると、NANDゲート250abの出力 LP1が立ち下がり、この奇数番目のラッチパルスLP の立ち下がりにより出力LP1が立ち上がる。また偶数 番目のラッチパルスLPが立ち上がると、NANDゲー 30 ト250 a c の出力 L P 2 が立ち下がり、この偶数番目 のラッチパルスLPの立ち上がりにより出力LP2が立 ち上がる。従って、出力LP1、LP2は交互に出力さ れることになる。偶奇ライン識別回路250aは、モジ ュール・コントローラ100等で作成されたラッチパル スLPから偶奇ライン毎のラッチパルスLP1, LP2 を作成する。

【0057】本例においては、前述したように均等分散 型2ライン同時選択駆動方式であるので、2<sup>1</sup> = 2の数 だけ走査電極の電圧パルスパターンがあるが、2つの異 なる列パターンを連続した2本の走査電極に印加するよ うにしてあるので、そのパターン数を展開するには2フ ィールドが必要である。他方、フレーム毎に交流化信号 FRが反転するため、これも考慮すると、4フィールド ですべての列パターンが展開されることになる。このた め、周辺回路には走査電極の電位パターンを指定するフ ィールド・ステート回路250cが設けられている。な お、この電位パターンの指定情報はXドライバ内で発生 させずに、走査電極ドライバ側のコード発生部221又 50 はモジュール・コントロー100から受けるようにする

10

30

40

23

こともできる。このフィールド・ステート回路250 c は、フレーム開始パルスYDの逆相パルスによってリセ ットされフィールド開始パルスFSの入来毎に記憶内容 の反転するD型フリップ・フロップ250caと、その Q出力と交流化信号FRを2入力とする論理積ゲート2 50cbと、D型フリップ・フロップ250caのQ (バー) 出力と交流化信号FRのインバータ250 c c を介した信号を2入力とする論理積ゲート250cd と、論理積ゲート250cb, 250cdの両出力を2 入力とする論理和ゲート250ceとから構成されてい る。インバータ250 c c の奇数ラインの読み出し時に 発生するラッチパルスLP1によってメモリセルC 2i-1, mの表示データ(オン・オフ情報)が信号パルス割 り出し回路258の1ビットのラッチ回路258-1m に取り込まれ、不一致数判定回路258-2mの下位ビ ット用排他的論理和ゲートEX1 に供給される。またこ れに引続き発生する偶数ラインのラッチパルスLP2に よってメモリセルC<sub>2i,m</sub>の表示データ(オン・オフ情 報)は直接不一致数判定回路258-2mの上位ビット 用排他的論理和ゲートEX2 に供給される。ラッチパル 20 スLP1,2は交互に出力されるのでラッチ回路258 -1と258-3のラッチ期間は互いにオーバーラップ 期間を持っており、両メモリセルの表示データ(オンー オン、オンーオフ、オフーオン、オフーオフ)は同時的 に不一致数判定回路25.8-2mへ供給される。また前 述の2本の走査電極の列パターンに相当する情報も不一 **致数判定回路258-2mに供給されているので、不一** 致数判定回路258-2mは表示データの2ビット情報 と走査電極の2ビット情報の桁不一致を検出する。2本 同時選択の場合は、2ビット出力であるので不一致数判。 定回路258-2mの出力はそのままコード化された不 一致数として扱うことができる。本例における採りうる 不一致数は0,1又は2である。不一致数判定回路25 8-2mで得られた2ビット情報はラッチ回路258-3mに取り込まれ、その不一致数信号はレベルシフタ2 59mで高論理振幅レベルの信号に変換される。そし て、電圧セレクタ260mのデコーダ260aはその不 一致数信号をデコードし、選択スイッチ260bのトラ ンジスタのいずれかを開閉させることにより、信号電極。 の電 $(-V_2, 0, V_2, 0)$ のいずれかが選択されることに なる。なお、本例では不一致数0のときは-V2、不一 致数1のときは0、不一致数2のときはV2 が選択され。 る。このようなXドライバの構成によって均等分散型2 ライン同時選択駆動が可能となる。また、不一致数を判 定しなくとも、前述のフレームメモリ出力とフィールド ・ステート回路259cの出力から直接デコードするよ な回路構成を採用しても良い。

【0058】以上の説明で本例におけるXドライバの答: 部の構成及び動作が理解されたことであろうが、図14\* のタイミングチャートを参照しつつフレームメモリの書:50 24

込み及び読み出し動作を説明する。モジュール・コント ローラ100のタイミング信号発生回路120によって 図14に示すようなフレーム開始パルスYD、ラッチパ ルスLPが発生する。フレーム開始パルスYDは1フレ ーム期間(1F)毎発生し、またラッチパルスLPは1 水平期間(1H)内に2回発生する。ここでは、1フレ ーム期間内にN個のラッチパルスが発生する。ラッチパ ルスLPの1周期内ではモジュール・コントローラ10 0から1走査ライン分の表示データDATA(WD<sub>i</sub>) がシフトクロックXSCLによってXドライバ250へ 転送されて来る。図14ではVRAM12内の表示デー タDATAのうち第3走査ライン目の表示データWD3 を除き他のすべての走査ライン目の表示データが変更さ れた場合の書込み・読み出し動作を示しているので、第 3 走査ライン目の表示データWD3の転送は新たに行わ れず、第3走査ライン目の表示データの表示動作はフレ ームメモリ252内の旧データを読み出すことにより達 成される。Xドライバ250のタイミング回路253に よって図14に示すような読み出し制御信号RD,シフ トクロック検出信号WE及び書込み制御信号WRも発生 する。モジュール・コントローラ100側で新データW D2の転送をXドライバ250に対して完了すると、前 述したようにシフトクロックXSCLの転送も中止され る。その後新データWD4以降の転送とシフトクロック XSCLの発振が行われる。シフトクロックXSCLの 転送が一時中止されると、前述したように、モジュール ・コントローラ100はスタンバイ期間Sに入るので、 タイミング回路253のシフトクロック検出回路253 -4がそれを検出してシフトクロック検出信号WEが発 生する。これによって書込み制御信号(W3)のみ発生 しない。まず、最初のラッチパルス(LN)が発生する と、1ライン目の表示データ(WD1)が次のラッチパ ルス (L1) の発生までの間 (1周期内) にXドライバ 250へ入来し、ラッチパルス(L1)の発生により書 込みレジスタ256に取り込まれてフレームメモリ25 2の該当行アドレスに書き込まれるが、最初のラッチパ ルス(LN)が発生から次のラッチパルス(L1)の発 生までの間には、フレームメモリ252から1ライン目 の旧データの読み出し動作が行われる。ラッチパルスL Pが発生すると、先ず第1番目のプリチャージ制御信号 PC1 (期間C):が発生してから書込み制御信号WR (期間A)、が発生し、しかる後、第2番目のプリチャー ジ制御信号PC2(期間C)が発生してから読み出し制 御信号RD(期間B)が発生するが、シフトクロックX SCLの発振がないと書込みモードは存在せず、読み出 し制御信号R1により1ライン目の旧データの読み出し 動作が行われる。この読み出し動作においては、行アド レスレジスタ257によって1ライン目の行アドレスが 指定され、次のラッチパルス (L1)の発生による奇数。 ラッチパルスLP.1により1ライン目の旧データがフレ

ームメモリ252から読み出されラッチ回路258-1 mに格納されて下位桁用排他的論理和ゲートEX1へ送 られる。この1ライン目の旧データのラッチの後そのラ ッチパルス(L1)により1ライン目の新データWD1 がフレームメモリへ書き込まれる。ここで、フレームメ モリ252への書込みは、1ライン640ドットのとき は入力レジスタ255から数100ns程度の1シフト クロックXSCLで行われるのではなく、バッファとし ての書込みレジスタ256からそれ以上の充分な時間

25

(数 $\mu$ s)をかけて1ライン分一挙に書き込むようにし ている。従って、大容量表示になるに従い、書込み速度 の高速化を要求されるが、ラッチパルスにより書込みレ ジスタ256を介して書込み動作を行うことが望まし い。ラッチパルスL2の周期内において、1ライン目の 新データWD1の書込みの後は、読み出し制御信号R2 により2ライン目の旧データの読み出しが行われ、上位 桁用排他的論理和ゲートEX2へ送られる。そして、偶 数ラインのラッチパルスLP2の発生により不一致数判 定回路258-2で得られた不一致数の2ビット情報が ラッチ回路258-3でラッチされ、前述したように、 電圧セレクタ260でいずれかの信号電圧が選択され、 1走査ライン目分と2走査ライン目分に関する信号電極 電位が液晶マトリクスに印加される。

【0059】このように、本例のXライバ252は、1 ラッチパルス周期内に同一の行アドレスに対する書込み モードと読み出しモードを分割し、旧データの読み出し 後に次のラッチパルスの発生により新データの書込みを 実行するようにしている。従って、表示データの書込み から読み出しまでは1フレーム期間(1F)である。

【0060】これはとりわけ複数ライン同時選択駆動方 式を採用する場合に必要となる。信号電極の駆動波形を 決める表示データを読み出し期間において該当するフレ ームメモリのデータは一部新データに変わっていると、 不一致判定回路258が旧データのラインと新データの ラインの組から意味のない表示態様となる信号電極の駆 動波形を決定してしまうからである。特に同時に全本数 を選択する場合もあるので、表示データの書込みから読 み出しまでは1フレーム期間(1F)必要となる。従っ て、表示をスクロールするときに発生が考えられる意味 のない表示態様を避けるには、選択本数を問わず、1フ レーム期間(1F)後に読み出すようにすれば良い。た だ、同時選択の本数が少ないきは、1フレーム期間(1) F)までは必要ない。1ラッチパルスLPの周期内で、 同一の行アドレスに対して読み出しモード後に書込み動 作を行うようにすることもできる。しかしながら、本例 においても充分な書込み期間を確保するために、フレー ムメモリに対する書込みはシフトクロックXSCLのタ イミングでなくラッチパルスLPのタイミングによって 書込みレジスタ256により行うようにしてあることか らも明らかなように、読み出しモード後に書込み動作を

(14)

10

26

行うと、書込み時間が充分確保されない事態や、自動パ ワーセーブのセット等のタイミングは厳しくなる。特に 複数ライン選択駆動方式では、ラッチパルス、シフトク ロック等が従来に比して必然的に逓倍的に高速化される ので、上記のモード順は採用し難くなる。まして大容量 表示になると一層難しくなる。従って、1ラッチパルス 周期内に同一の行アドレスに対する書込みモード後に1 回又は複数回の読み出しモードを実行させ、旧データの 読み出しから1フレーム期間後に新データの書込みを実 行するようにすることが望ましい。

【0061】上記実施例においては、均等分散型2ライ ン同時選択駆動方式を採用しているため、1水平期間内 にフレームメモリ内の2行ライン分の表示データを読み 出す必要があるので、1水平期間内に2発のラッチパル スLPが発生するようモジュール・コントローラ100 のタイミイグ信号発生回路120の分周比を設定してあ る。これは、フレームメモリのメモリマトリクスのセル 配列において表示マトリクスの信号電極の本数とフレー ムメモリの列アドレス数とが等しく、走査電極の本数と 行アドレス数とが等しい一般的な場合を前提としている 20 からである。しかしながら、図15に示すように、フレ ームメモリの列アドレス数を表示マトリクスの信号電極 の本数の2倍で行アドレス数を走査電極の本数の半分 (ブロック数) としたメモルセル配列のRAMを用いる 場合には、従来通り、1水平期間内に1回発生するラッ チパルスLPを利用することができる。即ち、ラッチパ ルスLPの発生により読み出しモードになると、例えば フレームメモリの奇数ワード線WL2iに繋がるメモリセ ルC<sub>2i,2m</sub>、C<sub>2i,(2i+1)</sub>から同時に1ライン目及び2 ライン目の表示データがセンスアンプ252mを介して 30 出力され、2 ライン分の表示データの読み出しが1 発の

- ラッチパルスLPだけで済む。このような回路構成で は、図13に示すような2ライン目の表示データが出力 されるまで1ライン目表示データを保持しておく待ち合 わせ用のラッチ回路258-1mを除くことができ、高 速化の傾向のある第1のラッチパルスLP1と第2のラ ッチパルスLP2とのタイミング調整が微妙にならず、 ドライバセル部分の回路構成の簡素化により複数同時選 択駆動方式の実用化に寄与する。

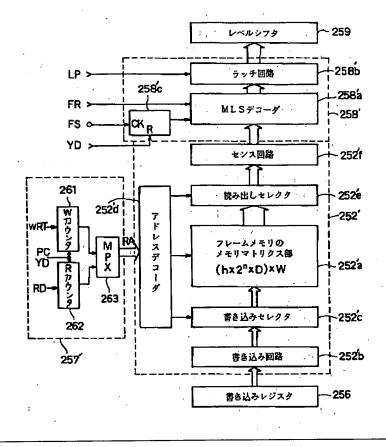

- 40 【0062】ただし、図16又は図15のメモリ構成の 場合、ラッチパルスLPの入力に対するフレームメモリ のワード線のアドレス歩進のスピードが書込みより読み 出しの方が速くなる。このため、図16に示すように、 行アドレスレジスタ257′は、書込みアドレス発生用 Wカウンタ261と読み出しアドレス発生用Rカウンタ 262とを独立に持っており、その出力をマルチプレク サ263で切り換え、マルチプレクサ263の出力RA をアドレスデコーダ252′dへ与える。書込みアドレ ス発生用Wカウンタ261は、フレーム開始パルスYD

50 で初期化され、図12で示されるプリチャージ信号PC

と書込み制御信号WRTを使って書込みアドレスを生成 する。また、読み出しアドレス発生用Rカウンタ262 は、フレーム開始パルスYDで初期化され、図12で示 されるプリチャージ信号PCと読み出し制御信号RDを 使って読み出しアドレスを生成する。このようにするこ とによって、2<sup>n</sup>本複数ライン同時選択駆動の場合は、 同時選択ライン数に関係なく、従来方式のコントローラ と同じラッチパルスLPの周期で表示データをコントロ ーラからXドライバに転送することができる。

27

【0063】ここで、上記2ライン同時読み出しの手法 を一般化し、複数ライン同時選択駆動方式において複数 ライン分の表示データをフレームメモリから同時に読み 出すXドライバの全体構成を図16を参照して簡単に説 明しておく。まずフレームメモリ252'のメモリマト リクス部252' aの縦横構成を(h×2<sup>n</sup>×D)×W とする。ここで、

h: 複数ライン同時選択駆動において同時選択駆動され る走査電極の本数

n:自然数

D:Xドライバ1個当りのドライバ出力数(駆動できる 信号電極の本数)

W:ワード線の本数

(h×2<sup>n</sup>×D)×Wは、Xドライバ1個が駆動できる 最大表示ドット数に等しい。因みに、図11のフレーム メモリ構成は(ドライバ出力数)×(表示ライン数)で ある。

【0064】図16において、書込みレジスタ256に 蓄えられた表示データは書込み制御信号WRに従って書 込み回路252′ bと書込みセレクタ252′ cを介し てアドレスデコーダ252' dで選択されたワード線に 繋がるメモリセルに書き込まれる。アドレスデコーダ2 52' dは図11の行アドレスシフトレジスタ257か ら出力される行アドレスをデコードするものである。表 示データの読み出し動作においては、読み出し制御信号 RDに従って(h×2<sup>n</sup>×D)ビットの表示データがフ レームメモリのメモリマトリクス部252' a から読み 出しセレクタ252' eに読み出される。読み出しセレ クタ252′ eはアドレスデコーダ252′ dの出力に 従って(h×2n×D)ビットのデータを選択する。従 って、n=0のときは読み出しセレクタ252' eは不 要となる。(h×D)ビットの表示データは、1 走査期 間にXドライバにより同時駆動される全表示データであ る。読み出しセレクタ252'eの出力はセンス回路2. 52' fによりディジタル信号に変換され、信号パルス 割り出し回路258′の複数同時選択駆動用デコーダ (MLSデコーダ) 25'8' aに送られる。MLSデコ ーダ258′aは、表示データ,液晶交流化信号FR, 走査スタート信号YDによりリセットされ、Yドライバ からのキャリー信号FSをカウントし、1フレーム内の 走査状態を区別するステートカウンタ258' cからの 50

(15)

10

28.

出力を受けて、ドライバ出力電位を選択する信号をデコ ードする。MLSデコーダ258' aの出力はラッチパ ルスLPをクロックとするラッチ回路258' bにより 同期がとられ、レベルシフタ259へ与えられる。この ような回路構成によれば、複数同時選択駆動方式と言え ども、複数ライン分の表示データの読み出しが1走査当 り1回で済むことになり、消費電力の削減効果と共に、 回路タイミングの単純化も実現できる。

【0065】なお、本例においては均等分散型2ライン 同時選択駆動方式を採用する場合を特に説明してある

が、本発明は3ライン以上の複数ラインを同時に選択す る駆動方式の場合にも適用できる。また本発明は部分的 に従来から用いられている電圧平均化法の駆動方式にも 適用できることは言う迄もない。更に、単純マトリクス 型に限らず、MIM駆動方式等にも適用できる。上記実 施例では、フレームメモリは表示体の画素に1対1に対 応するセルを持たせてあるが、表示体画素のうち現在駆 動されている画素の前後に関係する一部分又は複数画面 分のフレームメモリを持ち、間欠的に表示データをモジ ュール・コントローラからXドライバに送る方式や、表 20 示体の画素に対して圧縮された表示データを用いる方式 についても、本発明を適用できるところである。また更 に、本発明は、LCD表示装置に限らず、蛍光表示管, プラズマディスプレイ,エレクトロルミネッセンス等の マトリクス型ディスプレイや液晶のライトバルブ性を用 いた液晶応用装置等にも広く適用できるものである。

[0066]

【発明の効果】以上説明したように、本発明は、従来の マトリクス型表示制御装置と、従来のメモリ内蔵型の信 50 号電極ドライバとを組合せた方式において、マトリクス 型表示制御装置の高周波クロックの発振源を表示データ の転送の際に間欠動作させるようにしたことに特徴を有 する。このようなマトリクス型表示制御装置によれば、 第1の記憶手段において表示データの変更があったとき だけ高周波クロックが動作し、表示データを第2の記憶 手段へ転送するものであるから、高周波クロックの間欠 動作によりマトリクス表示装置全体の低消費電力化を図 ることができる。

.

【0067】また第2の記憶手段に対する転送処理はM

PUが行うのではなく、仲介に立つマトリクス表示制御、装置が実行するものであるため、第1の記憶手段側のホストMPUの処理負担を低減できると共に、更に信号電極の駆動装置をカスケード接続することにより、第2の記憶手段に走査ライン毎の表示データが一挙に格納されるので、アドレスの対応付けの容易化も達成でき、従って、画面変更の高速化を達成できる。更に、信号電極の駆動装置のカスケード接続により大容量表示装置でもマトリクス型表示制御装置と駆動装置との結線数を抑制でき、表示画面面積比率の大きな表示装置を実現できる。

【0068】また、信号電極ドライバにおいては高速ク

'n

,

|                                                          |      | 30                                                        |

|----------------------------------------------------------|------|-----------------------------------------------------------|

| 29<br>- たち 田いかいです ま本期間な八割! たタイミングで                       |      | 路図である。                                                    |

| ロックを用いないで1走査期間を分割したタイミングで                                |      | 【図14】同信号電極駆動回路における書込み動作及び                                 |

| 第2の記憶手段に余裕を以てアクセスするようにしてあ<br>る。                          |      | [図14] 向信々電磁派動回路におりる音が少勤「「次0<br>読み出し動作を説明するためのタイミングチャートであ  |

| る。<br>【0069】このため、第2の記憶手段へのアクセスタ                          |      | る。                                                        |

| イミングが従来に比して緩和されるので、書込み力を向                                |      | 【図15】同信号電極駆動回路における別のフレームッ                                 |

| イミングが促来に比して緩和されるので、音之のグレート上させることができ、第2の記憶手段の構成トランジス      |      | メモリの構成を示すブロック図である。                                        |

| 上させることができ、第2001億千段の構成「ノンシンハ<br>タのサイズを縮小化できる。ドライバのチップサイズの |      | 【図16】別のフレームッメモリを用いた場合における                                 |

| ·                                                        |      | 信号電極駆動回路(Xドライバ)の構成を示すブロック                                 |

| 小型化にも寄与する。<br>【0070】更に、本発明を複数ライン同時選択駆動方                  |      | 図である。                                                     |

| (0070) 更に、本先明を複数ノイン同時度(派動)が<br>法に適用すれば、1ライン当たりの表示に要するデータ | • 10 | 【符号の説明】                                                   |

|                                                          | 10   | 10…ホストMPU                                                 |

| 処理重が従来の駆動力法よりも多いにも持ちり、次小家<br>置自体を低周波で動作させるこができるので、従来より   |      | 11…システムメモリ                                                |

| 直日体を低周波で動作させるこかできるので、従来より<br>も低消費電力で、フリッカーが少なく、高コントラスト   |      | 1 2 ··· V R AM                                            |

| も低相質電力で、ノリッカーが少なく、高コンドノスト・高速応答のマトリクス型液晶表示装置を実現するこが       |      | 13…補助記憶装置                                                 |

|                                                          |      | 14 a …システムバス                                              |

| できる。<br>【図面の簡単な説明】                                       |      | 146…専用バス                                                  |

| 【図面の間単な説明】<br>【図1】本発明の実施例に係る単純マトリクス型液晶表                  |      | 15…入力用タッチセンサ                                              |

| 【図1】本発明の実施例にはる単純マトリシス全校曲衣<br>示装置の全体構成を示すブロック図である。        |      | 16…タッチセンサ・コントローラ                                          |

| 「設置の主体構成を示すプロシンムとのる。                                     |      | 17…データバス                                                  |

| 【図2】同実施内にはる単純(トリンハ生化師な小装置<br>におけるモジュール・コントローラの詳細を示すブロッ   | 20   | 100…モジュール・コントローラ                                          |

| ク図である。                                                   |      | 110…低周波発振回路                                               |

| ✓図てのる。<br>【図3】上記モジュール・コントローラの動作を説明す。                     |      | 110a…振動子                                                  |

| るためのタイミングチャートである。                                        |      | 120…タイミング信号発生回路                                           |

| 【図4】単純マトリクス型液晶表示装置における画素の                                |      | 121…分周器                                                   |

| オン・オフ態様の一例を示す模式図である。                                     |      | 122…垂直カウンタ                                                |

| 【図5】電圧平均化法によるマルチプレクス駆動方式に                                |      | 123…フレームカウンタ                                              |

| おける走査電極波形及び信号電極波形を示す波形図であ                                |      | 130…スタンバイ回路                                               |

| 3.                                                       |      | 131…システムバス・インターフェース回路                                     |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                     |      | 132…ラインフラグレジスタ                                            |

| おける画素液晶のオン・オフ特性を示す波形図である。                                | 30   | 133…比較回路                                                  |

| 【図7】均等分散型3ライン選択駆動方式における走査                                |      | 134…同期調整回路                                                |

| 電極波形及信号電極波形を示す波形図である。                                    | •    | 134a…インバータ                                                |

| 【図8】図7に示す均等分散型3ライン選択駆動方式に                                |      | 134b…D型フリップフロップ                                           |

| おける画素液晶のオン・オフ特性を示す波形図である。                                |      | 1 3 4 c …論理積ゲート                                           |

| 【図9】同実施例が採用する分散型2ライン選択駆動方                                |      | 140…高周波発振回路                                               |

| 式における走査電極波形及び信号電極波形の一例を示す                                |      | 141…論理積ゲート                                                |

| 波形図である。                                                  |      | 142…可変周波数CR発振器                                            |

| 【図10】(a)は同実施例に係る単純マトリクス型液                                |      | 1 4 2 a …論理積ゲート                                           |

| 晶表示装置における走査電極駆動回路(Y ドライバ)の                               |      | 142b, 142c…インバータ                                          |

| 構成を示すブロック図であり、(b)はその複数のYド                                | 40   | 142d…スイッチ選択レジスタ                                           |

| ライバをカスケード接続した結線図である。                                     | •    | R <sub>1</sub> , R <sub>2</sub> , R <sub>2</sub> …帰還抵抗    |

| 【図11】同実施例に係る単純マトリクス型液晶表示装                                |      | C1 …帰還キャパシタ                                               |

| 置における信号電極駆動回路 (Xドライバ)の構成を示                               | · ·  | SW <sub>1,</sub> SW <sub>2,</sub> SW <sub>3</sub> …選択スイッチ |

| すブロック図である。                                               |      | 143…間欠動作時限回路                                              |

| 【図12】同信号電極駆動回路(X ドライバ)における                               |      | 143a…インバータ                                                |

| タイミング回路の構成の詳細を示す回路図である。                                  |      | 143b…論理積ゲート                                               |

| 【図13】同信号電極駆動回路における周辺回路とフレ                                |      | 143c…プリセット・カウンタ                                           |

| ームメモリから信号パルス割り出し回路, レベルシフタ                               |      | 143 e…インバータ                                               |

| 及び電圧セレクタまでの1信号電極当り(1出力X <sub>m</sub> )                   |      | 143d…クロック数レジスタ                                            |

| のmビット回路部250mに着目した回路構成を示す叵                                | 50   | 143f…インバータ                                                |

|                                                          |      |                                                           |

.

.

. .

(17)

32 31 253a…論理積ゲート 144…論理積ゲート 253b…論理積ゲート 150…DMA回路 253c…論理積ゲート 151…DMA制御回路 253d, 253h, 253i…インバータ 152…データ変換回路 253e, 253f, 253g, 253g' ... NAND 200…LCDモジュール 220…Yドライバ ゲート 253i, 253k, 253m…遅延回路 221…コード発生部 253s, 253t…D型フリップフロップ 222…電圧セレクタ 223…第1シフトレジスタ EX1 EX2 …排他的論理和ゲート 10 254…データ入力制御回路 224…第2シフトレジスタ 255…入力レジスタ 225…ラッチ部 256…書込みレジスタ 226…レベルシフタ 257…行アドレスレジスタ 250…Xドライバ 258-…信号パルス割り出し回路 250a…偶奇ライン識別回路 258-1…ラッチ回路 250aa…D型フリップフロップ 258-2…不一致数判定回路 250ab, 250ac…NANDゲート 258-3…ラッチ回路 250c…フィールド・ステート回路 259…レベルシフタ 250ca…D型フリップフロップ 260…電圧セレクタ 250cb, 250cd…論理積ゲート 252' ā…フレームメモリ 250cc…インバータ 252′b…書込み回路 250ce…論理和ゲート ·2·5 2' c…書込みセレクタ 251…チップイネーブル・コントロール回路 252' d…アドレスデコーダ 252…フレームメモリ 2:5 2' e…読み出しセレクタ 253…タイミング回路 253-1…第1のワンショット・マルチバイブレータ 258/…信号パルス割り出し回路 258' a ... MSL デコーダ 253-2…第2のワンショット・マルチバイブレータ 258'b…ラッチ回路 253-3…第3のワンショット・マルチバイフ 258' c…ステートカウンタ。 253-4…シフトクロック検出回路 253-5…論理積グ

【図4】

特開平6-130910・

時間

• • • •

(特開平,6-130910)

特開平6-130910

(22)

【図12】

;

(24)

## 【図15】

【図16】

【手続補正書】 【提出日】平成5年7月13日 【手続補正1】 【補正対象書類名】明細書 【補正対象項目名】0002 【補正方法】変更 【補正内容】

【従来の技術】従来、フラットディスプレイの一例とし ての単純マトリクス型液晶表示装置においては、MPU (マイクロ・プロセッサ・ユニット)側から表示データ をLCDモジュール(液晶表示パネル(LCDパネ ル),走査電極駆動回路(Yドライバ),信号電極駆動, 回路(Xドライバ)等)へ転送する方式として、マトリ クス型液晶表示素子モジュール・コントローラ(以下、 モジュール・コントローラと言う)を用いる方式と<u>RA</u> <u>M(データ読み出し用)</u>内蔵型Xドライバを用いる方式 とに大別できる。まず、前者の方式は、CRTを用いた 表示装置と同様、システムバスに繋がるモジュール・コ ントローラが表示データを記憶しているビデオRAM (VRAM)から表示データを読み出し、これをLCD: モジュールに対し高周波数のクロックで転送して表示リー フレッシュ動作を行うものである。後者の方式は、Xド ライバ内に2ポートタイプのフレームメモリ(内蔵RA M)を持ち、MPUがデータバス、コントロールバス又 はアドレスバスを介して液晶表示タイミングとは無関係 に直接フレームメモリにアクセスし、フレームメモリ内 の表示データを変更するようになっており、Xドライバ 内で所要の制御信号を生成して、内蔵フレームメモリか らー走査ライン分の表示データを同時に読み出し、表示 リフレッシュ動作を行うものである。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0054

【補正方法】変更

【補正内容】。

【0054】シフトクロック検出回路253-4は、シ フトクロックXSCLの逆相クロックをリセット入力R (バー)とすると共に、ラッチパルスLPの反転クロッ クの立ち上がりで接地電位、(低レベル)をデータ反転入 力D:(バー)として記憶するD型フリップ・フロップ2 53sと、ラッチパルスLPの反転久ロックの立ち上が りでD型ブリップ・フロップ253\*sの反転出力Q:(バ ー)をズータ反転入力D:(バー)として記憶するD型フ リップ・フロップ253\*tを有している。シフトクロッ

クXSCLの入来があると、まず最初のシフトクロック XSCLのパルスでD型フリップ・フロップ253sが リセットされ、そのQ(バー)出力が高レベルとなって いるが、ラッチパルスLPの立ち下がりによってD型フ リップ・フロップ253sには接地電位がデータ反転入 カD(バー)として記憶されるのでそのQ(バー)出力 が低レベルへ遷移すると共に、D型フリップ・フロップ <u>253tには、253sの出力が変化する前の値が取り</u> 込まれ高レベルのデータ反転入力D(バー)を記憶する ので、そのQ(バー)出力たるシフトクロック検出信号 WEが高レベルとなる。ラッチパルスLP直後のシフト <u>クロックXSCLの入来すると、D型フリップ・フロッ</u> プ253sはリセットされ、そのQ(バー)出力が高レ ベルに戻る。このようにシフトクロックXSCLの入来 が続く限り、D型フリップ・フロップ253tからのシ フトクロック検出信号WEは高レベルであるので、論理 積ゲート253-5は導通状態のままであり、第2のワ ンショット・マルチバイブレータ253-2からの書込 み制御信号WRはフレームメモリ等へ出力され続ける。 他方、シフトクロックXSCLの入来が止み、最後のシ フトクロックXSCLのパルスでD型フリップ・フロッ プ253sのQ(バー)出力が低レベルに設定された状 態のままでラッチパルスLPが入来すると、D型フリッ プ・フロップ253tからのシフトクロック検出信号W Eが低レベルになるので、論理ゲート253-5が閉 じ、書込み制御信号WRの通過が禁止される。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0055 【補正方法】変更

【補正内容】

【0055】次に、図13を参照しつつXドライバ25 0における周辺回路とフレームメモリ252から信号パ ルス割り出し回路258、レベルシフタ259及び電圧 セレクタ260までの1信号電極当り(1出力Xm)の mビット回路部250mに着目した回路構成を説明す る。フレームメモリ252のメモリマトリクスにおける 奇数<u>ワード線WL2i-1</u>,偶数<u>ワード線WLi</u>とビット線 BL<sub>m</sub>, BL<sub>m</sub> (バー) との交点にはメモリセルC 2i-1, m、C<sub>2i,m</sub> があり、画素 P<sub>2i-1,m</sub>、 P<sub>2i,m</sub> に対 応した表示データ(オン・オフ情報)が格納されてい る。ラッチパルスLPが発生すると、タイミング回路2 53からプリチャージ信号PC, 書込み制御信号WR又 は読み出し制御信号RDが生成されるので、フレームメ モリ252への印加により奇数ワード線WL2i-1が行ア ドレスレジスタ257の順次的な指定によりフレームメ モリ252内の行アドレスデコーダによって選択され、 メモリセルC2i-1.mについての書込み又は読み出しが行 われる。また次のラッチパルスLPが発生すると、偶数 <u>ワード線WL</u>i が選択され、メモリセルC<sub>2i.m</sub>について

の書込み又は読み出しが行われる。なお、読み出し動作 においては読み出し制御信号RDによりセンス回路25 2mが能動化され、メモリセルから表示データが出力される。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0057

【補正方法】変更

【補正内容】

【0057】本例においては、前述したように均等分散 型2ライン同時選択駆動方式であるので、2<sup>1</sup> =2の数 だけ走査電極の電圧パルスパターンがあるが、2つの異 なる列パターンを連続した2本の走査電極に印加するよ うにしてあるので、そのパターン数を展開するには2フ イールドが必要である。他方、フレーム毎に交流化信号 FRが反転するため、これも考慮すると、4フィールド ですべての列パターンが展開されることになる。このた め、周辺回路には走査電極の電位パターンを指定するフ ィールド・ステート回路250cが設けられている。な お、この電位パターンの指定情報はXドライバ内で発生 させずに、走査電極ドライバ側のコード発生部221又 はモジュール・コントロー100から受けるようにする こともできる。このフィールド・ステート回路250c は、フレーム開始パルスYDの逆相パルスによってリセ ットされフィールド開始パルスFSの入来毎に記憶内容 の反転するD型フリップ・フロップ250caと、その Q出力と交流化信号FRを2入力とする論理積ゲート2 50cbと、D型フリップ・フロップ250caのQ (バー) 出力と交流化信号FRのインバータ250cc を介した信号を2入力とする論理積ゲート250cd と、論理積ゲート250cb, 250cdの両出力を2 入力とする論理和ゲート250ceとから構成されてい る。<u>奇数ラインの読み出し</u>時に発生するラッチパルスL P1によってメモリセルC2i-1.mの表示データ(オン・ オフ情報)が信号パルス割り出し回路258の1ビット のラッチ回路258-1mに取り込まれ、不一致数判定 回路258-2mの下位ビット用排他的論理和ゲートE X1 に供給される。またこれに引続き発生する偶数ライ ンのラッチパルスLP2によってメモリセルC<sub>2i.m</sub>の表 示データ(オン・オフ情報)は直接不一致数判定回路2 58-2mの上位ビット用排他的論理和ゲートEX2に 供給される。ラッチパルスLP1, 2は交互に出力され るのでラッチ回路258-1と258-3のラッチ期間 は互いにオーバーラップ期間を持っており、両メモリセ ルの表示データ(オンーオン、オンーオフ、オフーオ ン、オフーオフ)は同時的に不一致数判定回路258-2mへ供給される。また前述の2本の走査電極の列パタ ーンに相当する情報も不一致数判定回路258-2mに 供給されているので、不一致数判定回路258-2mは 表示データの2ビット情報と走査電極の2ビット情報の (27)

桁不一致を検出する。2本同時選択の場合は、2ビット 出力であるので不一致数判定回路258-2mの出力は そのままコード化された不一致数として扱うことができ る。本例における採りうる不一致数は0, 1又は2であ る。不一致数判定回路258-2mで得られた2ビット 情報はラッチ回路258-3mに取り込まれ、その不一 致数信号はレベルシフタ259mで高論理振幅レベルの 信号に変換される。そして、電圧セレクタ260mのデ コーダ260aはその不一致数信号をデコードし、選択 スイッチ260bのトランジスタのいずれかを開閉させ ることにより、信号電極の電位-V2, 0, V2 のいず れかが選択されることになる。なお、本例では不一致数 0のときは-V2、不一致数1のときは0、不一致数2 のときはV2 が選択される。このようなXドライバの構 成によって均等分散型2ライン同時選択駆動が可能とな る。また、不一致数を判定しなくとも、前述のフレーム メモリ出力とフィールド・ステート回路259cの出力 から直接デコードするよな回路構成を採用しても良い。

【手続補正5】 【補正対象書類名】明細書

【補正対象項目名】0058

【補正方法】変更

【補正内容】

【0058】以上の説明で本例におけるXドライバの各 部の構成及び動作が理解されたことであろうが、図14 のタイミングチャートを参照しつつフレームメモリの書 込み及び読み出し動作を説明する。モジュール・コント ローラ100のタイミング信号発生回路120によって 図14に示すようなフレーム開始パルスYD、ラッチパ ルスLPが発生する。フレーム開始パルスYDは1フレ ーム期間(1F)毎発生し、またラッチパルスLPは1 水平期間(1H)内に2回発生する。ここでは、1フレ ーム期間内にN個のラッチパルスが発生する。ラッチパ ルスLPの1周期内ではモジュール・コントローラ10 0から1走査ライン分の表示データDATA(WD<sub>i</sub>) がシフトクロックXSCLによってXドライバ250ヘ 転送されて来る。図14ではVRAM12内の表示デー タDATAのうち第3走査ライン目の表示データWD3 を除き他のすべての走査ライン目の表示データが変更さ れた場合の書込み・読み出し動作を示しているので、第 3 走査ライン目の表示データWD3の転送は新たに行わ れず、第3走査ライン目の表示データの表示動作はフレ ームメモリ252内の旧データを読み出すことにより違い 成される。Xドライバ250のタイミング回路253に よって図14に示すような読み出し制御信号RD,シフ トクロック検出信号WE及び書込み制御信号WRも発生 する。モジュール・コントローラ100側で新データWt D2の転送をXドライバ250に対して完了すると、前 述したようにシフトクロックXSCLの転送も中止ざれ. る。その後新データWD4以降の転送とシフトクロック

XSCLの発振が行われる。シフトクロックXSCLの 転送が一時中止ざれると、前述したように、モジュール ・コントローラ100はスタンバイ期間Sに入るので、 タイミング回路253のシフトクロック検出回路253 ー4がそれを検出してシフトクロック検出信号WEが発 <u>生しない。</u>これによって書込み制御信号(W3)のみ発 生しない。まず、最初のラッチパルス(LN)が発生す ると、1ライン目の表示データ(WD1)が次のラッチ パルス(L1)の発生までの間(1周期内)にXドライ バ250へ入来し、ラッチパルス(L1)の発生により 書込みレジスタ256に取り込まれてフレームメモリ2 52の該当行アドレスに書き込まれるが、最初のラッチ パルス(LN)が発生から次のラッチパルス(L1)の 発生までの間には、フレームメモリ252から1ライン 目の旧データの読み出し動作が行われる。ラッチパルス LPが発生すると、先ず第1番目のプリチャージ制御信 号PC1 (期間C)が発生してから書込み制御信号WR (期間A)が発生し、しかる後、第2番目のプリチャー ジ制御信号PC2(期間C)が発生してから読み出し制 御信号RD(期間B)が発生するが、シフトクロックX SCLの発振がないと書込みモードは存在せず、読み出 し制御信号R1により1ライン目の旧データの読み出し 動作が行われる。この読み出し動作においては、行アド レスレジスタ257によって1ライン目の行アドレスが 指定され、次のラッチパルス(L1)の発生による奇数 ラッチパルスLP1により1ライン目の旧データがフレ ームメモリ252から読み出されラッチ回路258-1 mに格納されて下位桁用排他的論理和ゲートEX1へ送 られる。この1ライン目の旧データのラッチの後そのラ ッチパルス(L1)により1ライン目の新データWD1 がフレームメモリへ書き込まれる。ここで、フレームメ モリ252への書込みは、1ライン640ドットのとき は入力レジスタ255から数100ns程度の1シフト クロックXSCLで行われるのではなく、バッファとし ての書込みレジスタ256からそれ以上の充分な時間 (数µ s) をかけて1 ライン分一挙に書き込むようにし ている。従って、大容量表示になるに従い、書込み速度 の高速化を要求されるが、ラッチパルスにより書込みレ ジスタ256を介して書込み動作を行うことが望まし い。ラッチパルスL2の周期内において、1ライン目の 新データWD1の書込みの後は、読み出し制御信号R2 により2ライン目の旧データの読み出しが行われ、上位: 桁用排他的論理和ゲート EX2 へ送られる。そして、偶 数ラインのラッチパルスLP2の発生により不一致数判: 定回路258-2で得られた不一致数の2ビット情報が ラッチ回路258-3でラッチされ、前述したように、 電圧セレクタ260でいずれかの信号電圧が選択され、 ・1 走査ライン目分と2 走査ライン目分に関する信号電極 電位が液晶マトリクスに印加される。 【手続補正6】

【補正内容】

【図12】

【補正対象書類名】図面 【補正対象項目名】図12 【補正方法】変更

.

【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第2区分

【発行日】平成13年7月6日(2001.7.6)

【公開番号】特開平6-130910 【公開日】平成6年5月13日(1994.5.13) 【年通号数】公開特許公報6-1310 【出願番号】特願平5-152533 【国際特許分類第7版】

G09G 3/20 G02F 1/133 545 G09G 3/36 [FI] G09G 3/20 R G02F 1/133 545 G09G 3/36

【手続補正書】

【提出日】平成12年6月21日(2000.6.2 1)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】特許請求の範囲

【補正方法】変更

【補正内容】 【特許請求の範囲】

【請求項1】 表示画素がマトリクス状に配列されたマ トリクス型表示体と、表示データを記憶す<u>る第</u>1の記憶 手段と、該表示画素の少なくとも一部に対応する表示デ ータを記憶す<u>る第</u>2の記憶手段と、<u>前記</u>第2の記憶手段 から<u>読み出される</u>表示データ<u>に基づき</u>前記マトリクス表 示体<u>を駆動する</u>駆動手段とを有するマトリクス型表示装 置において、

前記第1の記憶手段に記憶された表示データの変更によ り発振する間欠動作型<u>の</u>発振手段と、<u>前記</u>発振手段から <u>のク</u>ロックを用いて前記第1の記憶手段から前記変更に 係る表示データを読み出し<u>て前</u>記第2の記憶手<u>段へ</u>転送 する表示データ転送手段とを有することを特徴とするマ トリクス型表示装置。

【請求項2】 第1の記憶手段に記憶された表示データ の変更により発振する間欠動作型の発振手段と、前記発 振手段からのクロックを用いて前記第1の記憶手段から 前記変更に係る表示データを読み出して第2の記憶手段 へ転送する表示データ転送手段とを有することを特徴と するマトリクス型表示制御装置。

【請求項3】 表示画素がマトリクス状に配列されたマ トリクス型表示体と、表示データを記憶する第1の記憶 手段と、該表示画素の少なくとも一部に対応する表示デ ータを記憶する第2の記憶手段と、前記第2の記憶手段 から読み出される表示データに基づき前記マトリクス表 <u>示体を駆動する駆動手段とを有するマトリクス型表示装</u> 置において、

<u>前記第1の記憶手段に記憶された表示データの変更により発振する間欠動作型の第1の発振手段と、</u>

<u>前記第1の発振手段よりも低周波数で発振する第2の発</u> 振手段と、

<u>前記第1の発振手段からのクロックを用いて前記第1の</u> <u>記憶手段から前記変更に係る表示データを読み出して前</u> <u>記第2の記憶手段へ転送する表示データ転送手段と、</u>

<u>前記第2の発振手段からのクロックを用いて前記マトリ</u> クス表示体を駆動するためのタイミング信号を生成する タイミング信号発生手段とを有することを特徴とするマ トリクス型表示装置。

【請求項4】 マトリクス型表示体の表示画素の少なく とも一部に対応する表示データを記憶する随時書込み読 み出し可能の記憶手段を有し、該記憶手段から表示デー タを読み出し前記マトリクス表示体の信号電極に駆動電 圧を印加するマトリクス型表示駆動装置において、

1 走査期間毎に受け取る周期信号を基に1 走査期間でタ イミングをずらした書込み制御信号及び読み出し制御信 号を生成するタイミング発生手段と、前<u>記記</u>憶手段の同。 一行アドレスに対する読み出し制御信号により読み出し 動作を実行した後<u>前記書込み制御信号により書込み動</u> 作を実行する書込み読み出し手段とを有することを特徴 とするマトリクス型表示駆動装置。

【請求項5】 請求項4に記載のマドリクス型表示駆動: 装置において、前記表示データの転送に用いられ<u>るクローックの停止を検出するクロック検出手段と、前記クロック</u> <u>ク検出手段の検出信号に基づいて</u>前記書込み制御信号の、 発生を<u>停止させる</u>書込み禁止制御手段とを有することを 特徴とするマトリクス型表示駆動装置。

,【請求項6】, 請求項5に記載のマトリクス型表示駆動。

(2)

10

20

50

装置において、前記書込み読み出し手段は、入力される 表示データを前<u>記クロックを用</u>いて少なくとも1走査ラ イン分格納する一時格納手段と、該一時格納手段の格納 表示データを前<u>記クロックの1周期以上の長い信号によ</u> り前<u>記記</u>億手段に書込み供給するバッファッ手段とを有 することを特徴とするマトリクス型表示駆動装置。

1

【請求項7】 請求項4至請求項6のいずれか一項に記 載のマトリクス型表示駆動装置において、<u>前記</u>書込み読 み出し手段は、前<u>記記</u>憶手段から読み出した表示データ と前記マトリクス表示体の走査電極の電圧状態とから前 記信号電極に印加すべき信号電圧を割り出す信号電圧状 態割り付け手段を有することを特徴とするマトリクス型 表示駆動装置。

【請求項8】 請求項7に記載のマトリクス型表示駆動 装置において、前記信号電圧割り付け手段は、前記記憶 手段から複数の走査ライン分の表示データを時分割で読 み出す手段と、読み出された表示データを相互に待ち合 わせる一時記憶手段と、前記マトリクス表示体の走査電 極の電圧状態を指定する走査状態指定手段と、読み出さ れた複数の走査ライン分の表示データと走査電極の選択 電圧状態とから駆動電圧を選択する電圧選択手段とを有 することを特徴とするマトリクス型表示駆動装置。

【請求項9】 請求項7に記載のマトリクス型表示駆動 装置において、前<u>記記</u>憶手段は、1行アドレスに対し前 記マトリクス表示体の複数の走査ライン分の表示データ を格納するメモリ配列を有しており、前記信号電圧状態 割り付け手段は、前記複数の走査ライン分の表示データ を一挙に読み出す手段と、前記マトリクス表示体の走査 電極の電圧状態を指定する走査状態指定手段と、読み出 された複数の走査ライン分の表示データと走査電極の選 択電圧状態とから駆動電圧を選択する電圧選択手段とを 有することを特徴とするマトリクス型表示駆動装置。

【請求項10】 <u>請求項7乃至請求項9のいずれか一項</u> に記載のマトリクス型表示駆動装置において、複数本の 走査<u>ライン</u>を同時に選択し<u>かつ前記同時に選択される</u> <u>走査ラインを1フレーム内に複数回に分けて選択する</u>こ とを特徴とするマドリクス型表示駆動装置。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0005

【補正方法】変更

【補正内容】

[0005]

【課題を解決するための手段】上記課題を解決するため に、本発明の講じた手段は、従来のモジュール・コント ローラ型の表示装置と、従来のフレームメモリ内蔵型の 信号電極ドライバとを組合せた方式において、モジュー ル・コントローラのクロックの発振源を表示データの転 送の際に間欠動作させるようにしたことに特徴を有す る。即ち、本発明は、表示画素がマトリクス状に配列さ

れたマトリクス型表示体と、表示データを記憶す<u>る第</u>1 の記憶手段と、表示画素の少なくとも一部に対応する表 示データを記憶す<u>る第</u>2の記憶手段と、第2の記憶手段 から<u>読み出される</u>表示データ<u>に基づき</u>前記マトリクス表 示体<u>を駆動する</u>駆動手段とを有するマトリクス型表示装 置において、第1の記憶手段に記憶された表示データの 変更により発振する間欠動作型<u>の</u>発振手段と、発振手段 から<u>のク</u>ロックを用いて前記第1の記憶手段から前記変 更に係る表示データを読み出し<u>て</u>第2の記憶手<u>段へ</u>転送 する表示データ転送手段とを有することを特徴とする。

2

【手続補正3】 【補正対象書類名】明細書

【補正対象項目名】0006

【補正方法】変更

【補正内容】

【0006】<u>また、本発明に係るマトリクス型表示制御</u> 装置は、第1の記憶手段に記憶された表示データの変更 により発振する間欠動作型の発振手段と、この発振手段 からのクロックを用いて第1の記憶手段から前記変更に 係る表示データを読み出して第2の記憶手段へ転送する

表示データ転送手段とを有することを特徴とする。

【手続補正4】 【補正対象書類名】明細書 【補正対象項目名】0007 【補正方法】変更

【補正内容】

【0007】上記構成とは別に、本発明は、表示画素が マトリクス状に配列されたマトリクス型表示体と、表示 データを記憶する第1の記憶手段と、表示画素の少なく とも一部に対応する表示データを記憶する第2の記憶手 30 段と、第2の記憶手段から読み出される表示データに基 づきマトリクス表示体を駆動する駆動手段とを有するマ トリクス型表示装置において、第1の記憶手段に記憶さ れた表示データの変更により発振する間欠動作型の第1 の発振手段と、第1の発振手段よりも低周波数で発振す る第2の発振手段と、第1の発振手段からのクロックを 用いて第1の記憶手段から前記変更に係る表示データを 読み出して第2の記憶手段へ転送する表示データ転送手 段と、第2の発振手段からのクロックを用いてマトリク ス表示体を駆動するためのタイミング信号を生成するタ 40

イミング信号発生手段とを有することを特徴とする。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0008

【補正方法】変更

【補正内容】

【0008】更に、本発明は、マトリクス型表示体の表

<u>示画素の少なくとも一部に対応する表示データを記憶する随時書込み読み出し可能の記憶手段を有し、この記憶</u>手段から表示データを読み出しマトリクス表示体の信号

(3)

10

<u>電極に駆動電圧を印加するマトリクス型表示駆動装置に おいて、1走査期間毎に受け取る周期信号を基に1走査</u> 期間でタイミングをずらした書込み制御信号及び読み出 し制御信号を生成するタイミング発生手段と、記憶手段 の同一行アドレスに対する読み出し制御信号により読み 出し動作を実行した後、書込み制御信号により書込み動 作を実行する書込み読み出し手段とを有することを特徴

とする。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0009

【補正方法】変更

【補正内容】

【0009】<u>ここで、表示データの転送に用いられるク ロックの停止を検出するクロック検出手段と、このクロ ック検出手段の検出信号に基づいて書込み制御信号の発 生を停止させる書込み禁止制御手段とを有することが望 ましい。斯かる場合、書込み読み出し手段は、入力され る表示データを前記クロックを用いて少なくとも1走査 ライン分格納する一時格納手段と、この一時格納手段の 格納表示データを前記クロックの1周期以上の長い信号 により記憶手段に書込み供給するバッファッ手段とを設 けることが望ましい。そして、書込み読み出し手段とし ては、記憶手段から読み出した表示データとマトリクス 表示体の走査電極の電圧状態とから信号電極に印加すべ</u> e justification and the

き信号電圧を割り出す信号電圧状態割り付け手段を有す る。この信号電圧割り付け手段としては、記憶手段から 複数の走査ライン分の表示データを時分割で読み出す手 段と、読み出された表示データを相互に待ち合わせる一 時記憶手段と、マトリクス表示体の走査電極の電圧状態 を指定する走査状態指定手段と、読み出された複数の走 査ライン分の表示データと走査電極の選択電圧状態とか ら駆動電圧を選択する電圧選択手段とを有する。記憶手 段としては、1行アドレスに対し前記マトリクス表示体 の複数の走査ライン分の表示データを格納するメモリ配 列を有しており、信号電圧状態割り付け手段としては、

複数の走査ライン分の表示データを一挙に読み出す手段 と、マトリクス表示体の走査電極の電圧状態を指定する 走査状態指定手段と、読み出された複数の走査ライン分 の表示データと走査電極の選択電圧状態とから駆動電圧 を選択する電圧選択手段とを有する。

【手続補正7】

【補正対象書類名】明細書

【補正対象項目名】0010

【補正方法】変更

【補正内容】

【0010】また、<u>マトリクス型表示駆動装置として</u> <u>は、</u>複数本の走査<u>ライン</u>を同時に選択し<u>かつ前記同時</u> <u>に選択される走査ラインを1フレーム内に複数回に分け</u> <u>て選択する</u>ことを特徴とする。

# PATENT ABSTRACTS OF JAPAN

(11)Publication number: 06-130910

(43)Date of publication of application : 13.05.1994

| (51)Int.CI.                                      |                         | G09G<br>G02F<br>G09G | 1/133      |                             |       |            |

|--------------------------------------------------|-------------------------|----------------------|------------|-----------------------------|-------|------------|

| (21)Application number :<br>(22)Date of filing : | 05–152533<br>24.06.1993 |                      |            | O EPSON CORP<br>IURA YOICHI |       |            |

|                                                  | · . ·                   | •.                   | <b>,</b> . | · . ·                       | · · · | <i>,</i> ` |

(30)Priority

Priority number : 04179997 Priority date : 07.07.1992 Priority country : JP

(54) MATRIX TYPE DISPLAY DEVICE, MATRIX TYPE DISPLAY CONTROLLER, AND MATRIX TYPE DISPLAY DRIVING DEVICE

(57)Abstract:

PURPOSE: To provide the matrix type display controller which has the display data transfer system improved and has a low power consumption and is adapted to large capacity display.

CONSTITUTION: A module controller 100 is provided with a low frequency oscillating circuit 110, a timing signal generating circuit 120 which generates a scan start signal YD or the like based on a low frequency clock fL of this circuit 110, a standby circuit 130 which monitors communication to a host MPU 10 and a system bus 14a and generates an intermittent operation start control signal ST for update of display data in a VRAM 12, a high frequency oscillating circuit 140 which generates a high frequency clock whose phase is synchronized with that of the low frequency clock fL, and a DMA circuit

150 which reads out display data from the VRAM 12 through a private bus 14b by direct memory access and transfers it to frame memories 252 of X drivers 250-1 to 250-N through a data bus 17.

|                                                                                                                                     | 1          |            |         | • • • • |         |

|-------------------------------------------------------------------------------------------------------------------------------------|------------|------------|---------|---------|---------|

| LEGAL STATUS                                                                                                                        |            | ·. ·       | · ·     | •. •    | ·<br>.• |

| [Date of request for examination]                                                                                                   | 21.06.2000 | · ·        | ن       | 54 A    |         |

| [Date of sending the examiner's decision of rejection]                                                                              | 06.04.2004 |            |         | •       | •       |

| [Kind of final disposal of application other than the<br>examiner's decision of rejection or application converted<br>registration] | 3          |            |         |         |         |

| [Date of final disposal for application]                                                                                            |            |            | · · · · |         |         |

| [Patent number]                                                                                                                     | 3582082    | • • • •    |         |         | · • •   |

| [Date of registration]                                                                                                              | 06.08.2004 |            |         | •       |         |

| [Number of appeal against examiner's decision of rejection]                                                                         |            | 1. ••. ••. |         | •       | •       |

| [Date of requesting appeal against examiner's decision of rejection]                                                                | 06.05.2004 |            |         |         | ·       |

| [Date of extinction of right]                                                                                                       |            |            |         |         |         |

Copyright (C); 1998,2003 Japan Patent Office

### \* NOTICES \*

9

JPO and NCIPI are not responsible for any

damages caused by the use of this translation.

1. This document has been translated by computer. So the translation may not reflect the original precisely.

2.\*\*\*\* shows the word which can not be translated. 3.In the drawings, any words are not translated.

### CLAIMS

#### [Claim(s)]

[Claim 1] The matrix mold display object with which the display pixel was arranged in the shape of a matrix, and 1st storage means in which write-in read-out is possible at any time to memorize an indicative data, 2nd storage means in which write-in read-out is possible at any time to memorize the indicative data corresponding to this a part of display pixel [ at least ], In the matrix mold display which has the signal-electrode driving means which reads an indicative data from the 2nd storage means, and impresses driver voltage to the signal electrode of said matrix display object An intermittent-control-action mold RF oscillation means to oscillate by modification of the indicative data transfer means to read the indicative data which starts said modification from said 1st storage means using the RF clock from this intermittent-control-action mold RF oscillation means side.

[Claim 2] The matrix mold display control characterized by to have an intermittent-control-action mold RF oscillation means to oscillate by modification of the indicative data memorized by the 1st storage means, and an indicative-data transfer means read the indicative data which starts said modification from said 1st storage means using the RF clock from this intermittent-control-action mold RF oscillation means, and transmit this and said RF clock to a 2nd storage means side.

[Claim 3] A low frequency oscillation means to always oscillate a low frequency clock, and a timing signal generating means to generate a necessary timing signal based on the low frequency clock from this low frequency oscillation means, A renewal detection means of an indicative data to generate an intermittent-control-action control signal by modification of the indicative data memorized by the 1st storage means, An intermittent-control-action mold RF oscillation means to oscillate with this intermittent-control-action control signal, The matrix mold display control characterized by having an indicative-data transfer means to read the indicative data which starts said modification from said 1st storage means using the RF clock from this intermittent-control-action mold RF oscillation means, and to transmit this and said RF clock to a 2nd storage means side.

[Claim 4] It has 2nd storage means in which write-in read-out is possible at any time to memorize the indicative data corresponding to a part of display pixel [ at least ] of a matrix mold display object. In the matrix mold display driving gear which reads an indicative data from the 2nd storage means, and impresses driver voltage to the signal electrode of said matrix display object A timing generating means to generate the write-in control signal and read-out control signal which shifted timing in one scan period based on the periodic signal received for every scan period, The matrix mold display driving gear characterized by having a write-in read-out means to perform write-in actuation with the account of back to front write-in control signal which performed read-out actuation with the read-out control signal over the same line address of said 2nd storage means.

[Claim 5] The matrix mold display driving gear characterized by having a clock detection means to detect a halt of the high-frequency clock used for a transfer of said indicative data of operation in a matrix mold display driving gear according to claim 4, and having the write-inhibit control means which prevents generating of said write-in control signal by this detecting signal.

[Claim 6] It is the matrix mold display driving gear characterized by having a temporary storage means to store at least the indicative data which carries out Iriki of said write-in read-out means in a matrix mold display driving gear according to claim 5 by 1 scan line, using said high-frequency clock one by one, and the BAFFATSU means which carries out write-in supply of the storing indicative data of this temporary storage means at said 2nd storage means with the long signal of one or more periods of said high frequency clock.

[Claim 7] It is the matrix mold display driving gear characterized by having a signal-level condition allotment means to deduce the signal level which should be impressed to said signal electrode from the indicative data which read the write-in read-out means from said 2nd storage means in the matrix mold display driving gear given in any 1 term of claim 4 \*\*\*\*\*\*\*\* 6, and the electrical-potential-difference condition of the scan electrode of said matrix display object.

[Claim 8] In a matrix mold display driving gear according to claim 7 said signal-level allotment means The means which reads two or more indicative datas for a scan line by time sharing from said 2nd storage means, A temporary storage means to wait the read indicative data mutually, and a scan condition assignment means to specify the electrical-potential-difference condition of the scan electrode of said matrix display object, The matrix mold display driving gear characterized by having a voltage selection means to choose driver voltage from two or more indicative datas for a scan line and the selection electrical-potential-difference which were read.

[Claim 9] In a matrix mold display driving gear according to claim 7 said 2nd storage means It has the memory array which stores two or more indicative datas for a scan line of said matrix display object to 1 line address. Said signal-level condition allotment means The means which reads said two or more indicative datas for a scan line at once, and a scan condition assignment means to specify the electrical-potential-difference condition of the scan electrode of said matrix display object. The matrix mold display driving gear characterized by having a voltage selection means to choose driver voltage from two or more indicative datas for a scan line and the selection electrical-potential-difference condition which were read.

[Claim 10] The matrix mold display driving gear characterized by having the means which chooses two or more scan electrodes as coincidence, and carries out the round scan of multiple times into the period of a frame start signal in the matrix mold display driving gear which chooses and drives the scan electrode of a matrix mold display object.

[Translation done.]

#### \* NOTICES \*

0

JPO and NCIPI are not responsible for any damages caused by the use of this translation.

1. This document has been translated by computer. So the translation may not reflect the original precisely.

2.\*\*\*\* shows the word which can not be translated.

3. In the drawings, any words are not translated.

#### DETAILED DESCRIPTION

[Detailed Description of the Invention] [0001]

. .

[Industrial Application] This invention mainly relates to amelioration of a matrix mold display device module controller and a signal-electrode driver circuit in more detail about matrix mold indicating equipments, such as a suitable liquid crystal display to adopt two or more line coincidence selection drive method.

#### [0002]

[Description of the Prior Art] In the simple matrix liquid crystal display as an example of a former and flat display As a method which transmits an indicative data to LCD modules (a liquid crystal display panel (LCD panel), a scan electrode drive circuit (Y driver), signal-electrode drive circuit (X driver), etc.) from the MPU (microprocessor unit) side It can divide roughly into the method using a matrix mold liquid crystal display component module controller (henceforth a module controller), and the method using a RAM (read-only memory) built-in X driver. First, the former method reads an indicative data from the Video RAM (VRAM) the module controller connected with a system bus like the indicating equipment which used CRT has remembered the indicative data to be, transmits this with the clock of high frequency to a LCD module, and display refresh actuation is performed. The latter method has the frame memory (built-in RAM) of two port types in X driver, and through a data bus, a control bus, or an address bus, liquid crystal display timing accesses a direct frame memory independently, and MPU changes the indicative data in a frame memory, generates a control signal necessary within X driver, reads the indicative data for 1 scan line from a built-in frame memory to coincidence, and performs display refresh actuation.

#### [0003]

[Problem(s) to be Solved by the Invention] In the former method, since read-out from VRAM and a transfer are performed according to the liquid crystal display timing whenever it changes the display screen, it is necessary to always operate VRAM, a module controller, and a liquid crystal driver by the high-frequency clock. Moreover, the circuit related to display refresh actuation covers VRAM, a module controller, and a liquid crystal driver. According to actuation of the large-scale circuit in this highfrequency clock, a penetration current etc. arises in CMOS of a large number which constitute a circuit element, and it leads to increase of power consumption, and if a large-sized LCD panel is used, it will increase so much. Moreover, although there are access of MPU and module Comte Lara's access to VRAM, while a high-speed clock must be used so that access of MPU at the time of display refresh actuation may not collide with access of MPU, and low frequency actuation-ization of a module controller has constraint, constraint is attached also to a MPU throughput. In the latter method, since a transfer of an indicative data is performed regardless of liquid crystal display timing, actuation with a low frequency clock is possible, and it ends with power consumption low figures double [1-] compared with the former method. By the way, although it is necessary to increase the number of X driver when using a large-sized liquid crystal panel By the internal memory (RAM) of X driver having the independent address space in itself, and generally describing the number of output terminals of X driver two, since it is multiples of 10, such as for example, 160 pins instead of \*\*\*\* (2n) When the internal memory of two or more X drivers is seen from the MPU side, a discrete opening arises in the address of the whole internal memory, and the continuity of the address is not secured in many cases. For this reason, when changing the whole display screen, such as scrolling actuation and panning actuation, into coincidence, it will be obliged to the need of processing address-mapping attachment by the MPU side at high speed, and MPU will be forced a big processing burden. Of course, although it can design so that the number of output pins of X driver IC may be described two and it may be made \*\*\*\*, adjustment with the number of electrodes of the existing liquid crystal panel collapses, and the compatibility of a system is spoiled remarkably. Moreover, if many X drivers are used, numbers, such as a chip select line, must increase inevitably, must secure that much the tooth space of X driver of a large number allotted around a liquid crystal panel, will cause the fall of the screen product ratio of a panel, and will become the failure of a miniaturization of a LCD module. Therefore, the latter method is unsuitable for applying to a large-scale liquid crystal panel.

[0004] Then, though it is a low power when this invention improves the transmittal mode of an indicative data in view of each above-mentioned trouble, it is in offering the matrix mold display control, matrix mold display driving gear, and matrix mold display suitable for a mass display.

#### [0005]

۵

[Means for Solving the Problem] In order to solve the above-mentioned technical problem, the means which this invention provided has the description in the method which combined the indicating equipment of the conventional module controller mold, and the conventional frame memory built-in signal-electrode driver for it to have been made to carry out the intermittent control action of the source of an oscillation of the high frequency clock of a module controller on the occasion of a transfer of an indicative data. Namely, the matrix mold display object with which, as for this invention, the display pixel was arranged in the shape of a matrix, 1st storage means in which write-in read-out is possible at any time to memorize an indicative data, 2nd storage means in which write-in read-out is possible at any time to memorize the indicative data corresponding to a part of display pixel [ at least ], In the matrix mold display which has the signal-electrode driving means which reads an indicative data from the 2nd storage means, and impresses driver voltage to the signal electrode of a matrix display object An intermittent-control-action mold RF oscillation means to oscillate a matrix mold display control by modification of the indicative data memorized by the 1st storage means, The indicative data which starts said modification from the 1st storage means using the high frequency clock from an intermittent-control-action mold high frequency oscillation means is read, and it has the description at the point constituted from this and an indicative-data transfer means to transmit a high frequency clock to said 2nd storage means side. The concrete configuration of this matrix mold display control A low frequency oscillation means to always oscillate a low frequency clock, and a timing signal generating means to generate a necessary timing signal based on the low frequency clock from a low frequency oscillation means, A renewal detection means of an indicative data to generate an intermittent-controlaction control signal by modification of the indicative data memorized by the 1st storage means, An intermittent-control-action mold RF oscillation means to oscillate with an intermittent-control-action control signal, The indicative data which starts modification from the 1st storage means using the high frequency clock from an intermittent-control-action mold high frequency oscillation means is read, and it has this and an indicative-data transfer means to transmit a high frequency clock to a 2nd storage means<sup>•</sup>side.

[0006] In the indicating equipment which has such a matrix mold display control, it has 2nd storage means in which write-in read-out is possible at any time to memorize the indicative data corresponding to a part of display pixel [ at least ]. As a matrix mold display driving gear which reads an indicative data from the 2nd storage means, and impresses driver voltage to the signal electrode of a matrix display object A timing generating means to generate the write-in control signal and read-out control signal which shifted timing in one scan period based on the periodic signal received for every scan period, It has a write-in read-out means to perform write-in actuation with the trailer lump control signal which performed read-out actuation with the read-out control signal over the same line address of the 2nd storage means.